您好!

我正在使用 F28384D 开发软件。

为了提高程序的速度、将其扩展为 RAM 并进行处理、而且通过使用 USB、RAM 的容量非常强大。

所以我考虑使用外部存储器。 我认为有多个访问外部存储器的选项(EMIF、SPI 等)。

哪种访问方法最快? 另外、如果我能做些什么来解决 RAM 容量紧张的问题、请告诉我。

谢谢。

Conor

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我正在使用 F28384D 开发软件。

为了提高程序的速度、将其扩展为 RAM 并进行处理、而且通过使用 USB、RAM 的容量非常强大。

所以我考虑使用外部存储器。 我认为有多个访问外部存储器的选项(EMIF、SPI 等)。

哪种访问方法最快? 另外、如果我能做些什么来解决 RAM 容量紧张的问题、请告诉我。

谢谢。

Conor

您好、Kier Vivek

问题1:

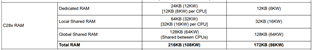

我有一个关于全局共享 RAM 的问题。 GSRAM0至15在链接器命令文件中定义。

是否可以将它们组合到一个存储器区域中?

问题2.

该问题与 Q1相关。

是否可以将全局共享 RAM、本地共享 RAM 和专用 RAM 组合到链接器命令文件的一个存储器区域中?

我的问题的背景是、我需要在 RAM 中放置一个大型程序、而全局共享 RAM (128KB)可能是不够的。

谢谢。

Conor

Unknown 说:q1.

我有一个关于全局共享 RAM 的问题。 GSRAM0至15在链接器命令文件中定义。

是否可以将它们组合到一个存储器区域?

可以。

Unknown 说:Q2.

该问题与 Q1相关。

是否可以将全局共享 RAM、本地共享 RAM 和专用 RAM 组合到链接器命令文件中的一个存储器区域中?

是的,但几乎肯定是一个坏主意。 如果您这样做、则无法控制段的位置。 一些节有一些限制。 例如、栈必须位于第一个64KiB 中。

我认为您需要在链接器文件中执行以下操作:

.text : >> RAMD0 | RAMD1 | RAMLS | RAMGS

您好、Kier

谢谢你。 我明白了。

有些部分有限制。 例如,堆栈必须位于前64KiB。

在哪里可以确定哪些部分有限制?

如果您有任何文档、请与我们分享。 我想知道、因为我计划在将来对该部分进行重大改变。

谢谢。

在哪里可以确定哪些部分有限制?

一个好的开始是编译器手册https://www.ti.com/lit/pdf/spru514中的"4.3.6指定在存储器中分配段的位置"部分

但还有其他外设注意事项。 例如、CLA 数据只能存储在 LSRAM 中。 据我所知、没有一个单独的文档介绍所有存储器放置注意事项。

即使它不是连续内存,它也可以排列吗?

是的、我相信是这样、但我不是100%确定。 您一定要尝试一下。