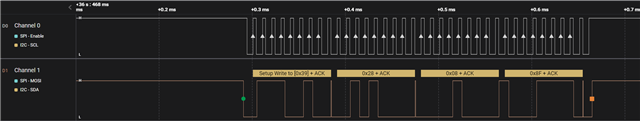

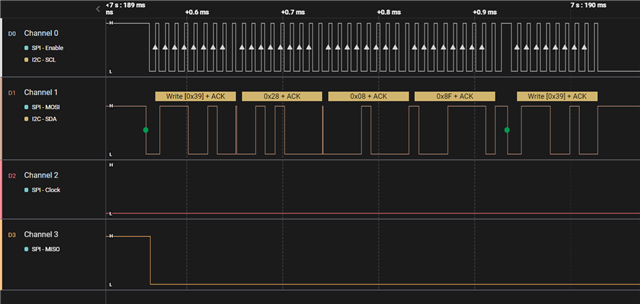

以下是正常的 IIC 交易。

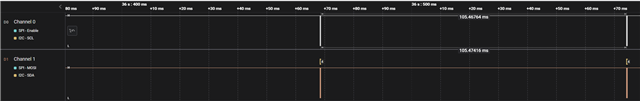

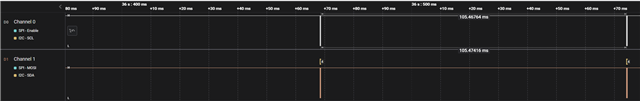

两次转换之间的延迟应为105ms。

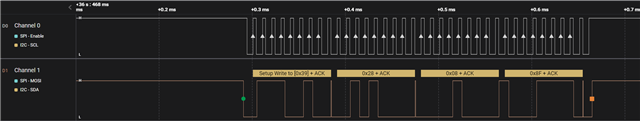

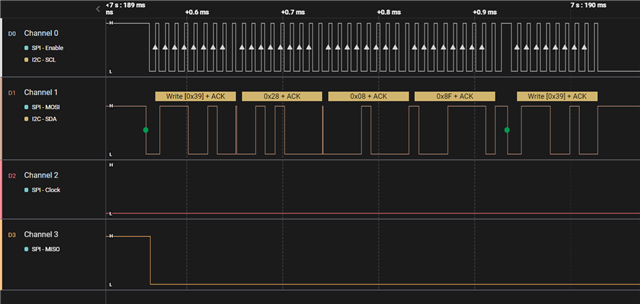

但我面临的错误,有时它将启动写通信非常非常接近,这是不是预期.

哪种方式可导致此错误? 其他中断?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

以下是正常的 IIC 交易。

两次转换之间的延迟应为105ms。

但我面临的错误,有时它将启动写通信非常非常接近,这是不是预期.

哪种方式可导致此错误? 其他中断?

您好!

您使用什么来触发 I2C 通信? 您要使用什么配置来设置外设?

[quote userid="554284" url="~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1236823/tms320f28386d-iic 有时候它会非常非常接近地启动写通信您能否用接近的方式量化您的意思?

此致、

阿米尔·奥马尔

通过调用以下函数周期来触发 I2C 通信

void I2cWritePECMax20480_TmrDly(void)

{

uint32_t _uMDataBuf = 0;

uint32_t _uMdev_id = 0;

uint32_t _uMreg = 0;

uint32_t _uMcrc_data_out = 0;

uint32_t _uMcrc_data_in[3];

_uMdev_id = 0x39;

_uMreg = 0x28;

_uMDataBuf = 0x08;

_uMcrc_data_in[0] = ((_uMdev_id<<1) | 0x00);

_uMcrc_data_in[1] = _uMreg;

_uMcrc_data_in[2] = _uMDataBuf;

_uMcrc_data_out = PEC_CRC(_uMcrc_data_in,3);

//

// Setup number of bytes to send msgBuffer and address

//

I2C_setDataCount(I2CB_BASE, 3);

I2C_sendStopCondition(I2CB_BASE);

//

// Setup data to send

//

I2C_putData(I2CB_BASE, _uMreg);

I2C_putData(I2CB_BASE, _uMDataBuf);

I2C_putData(I2CB_BASE,_uMcrc_data_out);

//

// Send start as master transmitter

//

//I2C_setFIFOInterruptLevel(I2CB_BASE, I2C_FIFO_TX3, I2C_FIFO_RX16);

I2C_setConfig(I2CB_BASE, I2C_MASTER_SEND_MODE);

I2C_sendStartCondition(I2CB_BASE);

//I2C_sendStopCondition(I2CB_BASE);

DEVICE_DELAY_US(50000);

}

IIC 初始化低于

I2C_disableModule(I2CB_BASE);

//

// I2C configuration. Use a 100kHz I2CCLK with a 33% duty cycle.

//

I2C_initMaster(I2CB_BASE, DEVICE_SYSCLK_FREQ, 100000, I2C_DUTYCYCLE_33);

I2C_setConfig(I2CB_BASE, I2C_MASTER_SEND_MODE);

I2C_setSlaveAddress(I2CB_BASE, 0x0039);

I2C_disableLoopback(I2CB_BASE);

I2C_setBitCount(I2CB_BASE, I2C_BITCOUNT_8);

I2C_setAddressMode(I2CB_BASE, I2C_ADDR_MODE_7BITS);

//

// FIFO configuration

//

I2C_enableFIFO(I2CB_BASE);

//

// Enable stop condition and register-access-ready interrupts

//

I2C_enableInterrupt(I2CB_BASE, I2C_INT_STOP_CONDITION |

I2C_INT_REG_ACCESS_RDY);

I2C_clearInterruptStatus(I2CB_BASE, I2C_INT_ADDR_SLAVE | I2C_INT_ARB_LOST | I2C_INT_NO_ACK | I2C_INT_STOP_CONDITION);

I2C_setFIFOInterruptLevel(I2CB_BASE, I2C_FIFO_TX3, I2C_FIFO_RX16);

I2C_setEmulationMode(I2CB_BASE, I2C_EMULATION_FREE_RUN);

//

// Configuration complete. Enable the module.

//

I2C_enableModule(I2CB_BASE);[/报价]

- 在您的第一个代码片段的第21行、您为什么发送停止条件

- 您可以向我发送在发生这种额外写入时为 I2C 设置的状态位吗?

由于引用了 TI 的示例、我发送了一个停止条件。 I2C_ex4_EEPROM_Polling。 此停止是否会导致意外情况?

我使用逻辑分析仪捕获了额外的写入、如果需要状态位、我将添加中断来捕获这个额外的写入。

哪个中断可以捕获此错误? 我需要此信息来启用 I2C 中断。 如下所示。

I2C_enableInterrupt (I2CB_BASE、I2C_INT_STOP_Condition |

I2C_INT_REG_ACCESS_RDY);

您好!

我注意到您正在创建许多与 I2C 相同主题的线程。 请尝试将所有类似问题保存在一个主题中(如果需要、请花点时间编译并列出您在发布之前遇到的问题、而不是将每个问题发布为单独的主题)。 到目前为止、看起来 您已经创建了一些与 I2C 相关的线程。 这使得很难跟踪和尝试回答您的问题。

我将继续并合并这些内容、 尝试回答您的问题。 请避免在将来执行此操作。

此致、

阿米尔·奥马尔

您好!

第二个 ACK ((No-)接收方的确认位), 此接收器是否表示主接收器?

图片讨论的是 I2C 数据传输、因此我认为接收器是 F2838x 外部的目标器件。 但是、我认为这可以适用于任何一种方式; F2838x 或外部 I2C 器件可以是接收器、因为您可以有一个控制器或目标作为接收器。

由于参考了 TI 的示例,我发送了一个停止条件。 I2C_ex4_EEPROM_Polling。 此停止是否会导致意外结果?

我查看了这个示例、但 在函数中没有看到此类流程。 您能指出您专门从哪个函数复制吗? 在我查看的寄存器中、似乎在通信结束时发送了停止条件、而您的代码在发送启动条件之前设置了停止条件。

哪种中断可以捕获此错误?

我知道、对于这种类型的错误、没有特定的中断。 您可以在每次 I2C 通信结束时只将状态位读取到变量中 、并在那里有断点;当逻辑分析仪显示发生了额外的写入时、查看变量的值。

、但在这个中断中、I2C 什么也没有。 我没有找到与它们的任何连接。

I2C 是 处于中断还是只是正常函数? 您刚才引用的基于代码的示例没有中断、它仅使用轮询、因此这在具有可能主动中断 I2C 通信的中断的程序中可能并不理想。

此致、

阿米尔·奥马尔

此图像讨论的是 I2C 数据传输,因此我相信接收器是 F2838x 外部的目标器件。 但是、我认为这可以适用于任何一种方式; F2838x 或外部 I2C 器件可以是接收器、因为您可以有一个控制器或一个目标是接收器。

明白了意思。 谢谢。

我查看了这个示例、但 在函数中没有看到此类流程。 您能指出您专门从哪个函数复制吗? 在我查看的寄存器中、似乎在通信结束时发送了停止条件、而您的代码在发送启动条件之前设置了停止条件。

从 i2c_ex5_master_slave_interrupt

uint16_t I2C_MasterTransmitter(struct I2CHandle *I2C_Params)

{

uint16_t status;

uint32_t base = I2C_Params->base;

I2C_Params->numofSixteenByte = (I2C_Params->NumOfDataBytes) / I2C_FIFO_LEVEL;

I2C_Params->remainingBytes = (I2C_Params->NumOfDataBytes) % I2C_FIFO_LEVEL;

ASSERT(I2C_Params->NumOfDataBytes <= MAX_BUFFER_SIZE);

I2C_enableFIFO(base);

status = I2C_TransmitSlaveAddress_ControlBytes(I2C_Params);

if(status)

{

return status;

}

I2C_setDataCount(base, (I2C_Params->NumOfAddrBytes + I2C_Params->NumOfDataBytes));

I2C_sendStopCondition(base);

I2C_setFIFOInterruptLevel(base, I2C_FIFO_TXEMPTY, I2C_FIFO_RXFULL);

I2C_enableInterrupt(base, (I2C_INT_STOP_CONDITION | I2C_INT_ARB_LOST | I2C_INT_NO_ACK));

I2C_enableInterrupt(base, I2C_INT_TXFF);

I2C_clearInterruptStatus(base, I2C_INT_TXFF);

return SUCCESS;

}I2C 是 中断还是只是正常函数? 您引用的基于代码的示例没有中断、它仅使用轮询、因此这在具有可能主动中断 I2C 通信的中断的程序中可能并不理想。

我们使用轮询模式。 因为在 OUT 项目中禁止了额外的中断。 (定义了项目 SW 架构)

我们想知道 90KHZ ADC 中断 是如何影响 I2C 通信的,它是否会使它失去功能? 如何实现?

我们发现根本原因是、当有 ADC 中断并继续调用以下代码时、会导致错误。

I2C_sendStartCondition (I2CB_BASE);

I2C_sendStopCondition (I2CB_BASE);

我们可以通过以下代码重现错误、添加以下两个错误之间的1us 延迟

I2C_sendStartCondition (I2CB_BASE);

I2C_sendStopCondition (I2CB_BASE);

void I2cWritePECMax20480_TmrDly(void)

{

uint32_t _uMDataBuf = 0;

uint32_t _uMdev_id = 0;

uint32_t _uMreg = 0;

uint32_t _uMcrc_data_out = 0;

uint32_t _uMcrc_data_in[3];

_uMdev_id = 0x39;

_uMreg = 0x28;

_uMDataBuf = 0x08;

_uMcrc_data_in[0] = ((_uMdev_id<<1) | 0x00);

_uMcrc_data_in[1] = _uMreg;

_uMcrc_data_in[2] = _uMDataBuf;

_uMcrc_data_out = PEC_CRC(_uMcrc_data_in,3);

//

// Setup number of bytes to send msgBuffer and address

//

I2C_setDataCount(I2CB_BASE, 3);

//

// Setup data to send

//

I2C_putData(I2CB_BASE, _uMreg);

I2C_putData(I2CB_BASE, _uMDataBuf);

I2C_putData(I2CB_BASE,_uMcrc_data_out);

//

// Send start as master transmitter

//

//I2C_setFIFOInterruptLevel(I2CB_BASE, I2C_FIFO_TX3, I2C_FIFO_RX16);

I2C_setConfig(I2CB_BASE, I2C_MASTER_SEND_MODE);

I2C_sendStartCondition(I2CB_BASE);

DINT;

DRTM;

DELAY_US(1);

I2C_sendStopCondition(I2CB_BASE);

DEVICE_DELAY_US(50000);

}

我们尝试将 I2C_sendStartCondition 和 I2C_sendStopCondition 合并 为一个代码。

它会解决问题并修复错误。

HWREGH (I2CB_BASE + I2C_O_MDR)|=(I2C_MDR_STT |I2C_MDR_STP);

如果 TI 的任何专家能够帮助您讨论这一点、我们将不胜感激。

您好!

当在 CPU2中添加 I2CB 时、 有时会显示 NACK 发生。

我想知道 NACK 发生的根本原因。

我应检查哪些寄存器来确认根本原因?

[/报价]好像您正在尝试在控制器发送器模式下使用 I2C 并从目标器件接收 NACK。 似乎目标 I2C 器件正在处理已发送的信息并阻止 F2837xD I2C 发送更多数据字节。 这是预期的行为、而不是器件错误。 NACK 信号来自 I2C 目标器件、因此、您需要查看所连接的 I2C 目标器件、而不是 F2837xD 器件。

来自 i2c_ex5_master_slave_interrupt您引用的代码片段在停止条件之后不会发送任何启动条件、 看起来此函数 专门用于将器件配置为控制器发送器、实际上并没有在该函数内发送任何内容。

我们想知道 90KHZ ADC 中断是如何 影响 I2C 通信的,它会不会使它变得不可用? 如何?您需要配置一些输出切换或观察变量以进行确认、但 ADC 中断会中断 I2C 通信并导致一些不同的行为。 我不知道 设计中具体是如何实现的、但根据其声音、如果您在使用轮询 I2C 时不使用中断、则没有问题。 我将与一些 中断专家确认、看看他们是否更了解这一点、但现在您 可以确认这是否是正在发生的情况。

如果来自 TI 的任何专家可以帮助交谈,我们不胜感激。这是一个与先前的问题不同的问题吗? 如果是、您能否说明实际问题是什么? 我不确定我是否理解你的最新帖子。

此致、

阿米尔·奥马尔

[/quote]

我们可以通过以下代码重现错误,在[/报价]之间添加1us 延迟这正是我希望 TI 专家能够确认的

[/quote]我们尝试将 I2C_sendStartCondition 和 I2C_sendStopCondition 合并 为一个代码。

它会解决问题并修复错误。

HWREGH (I2CB_BASE + I2C_O_MDR)|=(I2C_MDR_STT |I2C_MDR_STP);

[/报价]

您好!

我很确定没有其他启动条件发送。

请仔细检查、 您也可以读取 I2CSTR 寄存器中的总线繁忙位、查看当您即将发送另一个启动条件时它是否仍在传输过程中。

我将复制的错误步骤放在上面。

使用 I2C 轮询模式和其他中断的某个人可能具有相同的错误。

[/报价]任何其他客户均未报告此问题、因此不存在已知问题/修复。 您需要自行完成一些工作、以验证是否以某种方式发送了另一个启动、或者 您的代码是否在前一次传输的中间发送了另一个启动条件。

此致、

阿米尔·奥马尔