主题中讨论的其他器件:SysConfig

我希望通过 CMPSS ePWM CBC 跳匣区域控制功能实现死区延迟。

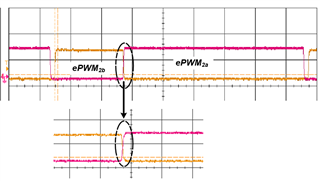

但当发生 TripZone 时、epwm2b 被强制为低电平、epwm2a 被强制为高电平(此时、我希望 epwm2a 上升沿延迟约为80ns)。

我知道正常的死区功能在这里不起作用。

参考:(e2e.ti.com/.../tms320f28384s-one-question-of-epwm-trip-zone-submodule)

因此、我将使用谷底开关功能、但它不起作用。 (其工作方式与下图类似)

示波器记录的波形。

有人能指导我吗?

我编写的代码是:

空 main (void)

{

InitSysCtrl ();//初始化器件时钟和外设

InitGpio();//初始化 GPIO

dint;//禁用 CPU 中断

InitPieCtrl ();//将 PIE 控制寄存器初始化为默认状态。

//禁用 CPU 中断并清除所有 CPU 中断标志:

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();//使用指向 shell 中断的指针初始化 PIE 向量表

setup1GPIO ();//用于启用 GPIO 的用户特定代码

// ADC (A4) CMPSS (CMP2)被选择(编号1415)

EALLOW;

AnalogSubsysRegs.CMPHPMXSEL.bit.CMP2HPMXSEL = 0;//IA-A4

EDIS;

//映射 ISR 函数

EALLOW;

PieVectTable.ADCA1_INT =&adcA1ISR;// ADCA 中断1的函数

EDIS;

initADC ();//配置 ADC 并启动

initEPWM1 (a);//配置 ePWM1

initEPWM2 (a);//配置 ePWM2

initEPWM3 (a);//配置 ePWM2

initADCSOC ();//在通道1上为 ePWM 触发的转换设置 ADC

CMPSSInit ();// CMPSS 已初始化。

XBARInit ();// XBAR 函数调用

//启用全局中断和更高优先级的实时调试事件:

IER |= M_INT1;//启用组1中断

EINT;//启用全局中断 INTM

ERTM;//启用全局实时中断 DBGM

PieCtrlRegs.PIEIER1.bit.INTx1 = 1;//启用 PIE 中断

//同步 ePWM

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;

//在循环中无限地进行转换

while (1)

{

//

//启动 ePWM

//

EPwm1Regs.ETSEL.bit.SOCAEN = 1;//启用 SOCA

EPwm1Regs.TBCTL.bit.CTRMODE = 0;//解冻、并进入向上计数模式

////空闲循环。 只需永久坐下并循环(可选):

////

for (;;)

{

__ asm (" NOP");

}

}

}

void initEPWM2 (UINT16周期)

{

EALLOW;

EPwm2Regs.TBPRD = a;//设置计时器周期

EPwm2Regs.TBPHS.bit.TBPHS = 0x0000;//相位为0

EPwm2Regs.TBCTR = 0x0000;

EPwm2Regs.TBCTL.bit.FREE_SOFT = 3;

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE;//禁用相位加载

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;//时钟与 SYSCLKOUT 的比率

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.SYNCOSEL=TB_CTR_ZERO;

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;//递增/递减计数

EPwm2Regs.TBCTL.bit.PRDLD = TB_shadow;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_HOLD;//每0加载一次寄存器

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_影子;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;// page.264

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm2Regs.DBCTL.bit.out_mode = DB_FULL_ENABLE;//启用死区模块

EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;//高电平有效互补模式(输出反相)

// EPwm2Regs.DBRED.bit.DBRED = DB;

EPwm2Regs.DBFED.bit.DBFED = DB;

//通过以下代码行,将 DB 延迟设置为 epwmB。

EPwm2Regs.CMPB.bit.CMPB = A-1;//设置比较

EPwm2Regs.AQCTLA.bit.CBU = AQ_SET;

EPwm2Regs.CMPA.bit.CMPA = A;

EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR;//AQ_CLEAR

// DCAH =比较器2输出

// DCAEVT2 = DCAH HI (将随着比较器输出变为 HI)>>>用于 epmwA

EPwm2Regs.DCTRIPSEL.bit.dCAHCOMPSEL = DC_TRIPIN4;//(页。 1980年)

EPwm2Regs.TZDCSEL.bit.dCAEVT2 = TZ_DCAH_HI;

EPwm2Regs.DCACTL.bit.EVT2SRCSEL = DC_EVT_FLT;// DCAEVT2 = DCAEVT2 (未滤波) DC_EVT2

EPwm2Regs.DCACTL.bit.EVT2FRCSYNCSEL = DC_EVT_ASYNC;//获取异步路径

EPwm2Regs.TZSEL.bit.dCAEVT2 = 1;

EPwm2Regs.TZCTL.bit.tZA = TZ_FORCE_HI;// EPWM1A 将变为低电平

//谷底开关。

//第1步。

EPwm2Regs.DCFCTL.bit.SRCSEL = 1;//数字滤波器输入源为 DCAEVT2。 (第1984号编)

//第2步。

EPwm2Regs.DCFCTL.bit.EDGEMODE = 0;// 0 =选择低边沿到高边沿(页号:1983)

// 1 =高到低

// 2 =两者

EPwm2Regs.DCFCTL.bit.EDGEUNT = 0;//更改值以验证(P.NO.1983)

//第3步。

EPwm2Regs.VCAPCTL.bit.TRIGSEL = 5;//捕获序列由 DCAEVT2事件触发。 (第1905号编)

//第4步。

EPwm2Regs.VCAPCTL.bit.VCAPE = 1;//启用谷底捕捉

//第5步。

EPwm2Regs.VCNTCFG.bit.STARTEDGE = 2 //(P.No.、

//第6步。

EPwm2Regs.VCNTCFG.bit.STOPEDGE = 3;//该值必须大于起始边沿。

//第7步。

EPwm2Regs.VCAPCTL.bit.VDELAYDIV =1;//HWVDELVAL = SWVDELVAL (P.NO.1905)

EPwm2Regs.SWVDELVAL = 5;//

//步骤8。

EPwm2Regs.VCAPCTL.bit.EDGEFILTDLYSEL = 1;//应用硬件谷值延迟(P.NO.1905)

// EPwm2Regs.HWVDELVAL = 5;//硬件谷底延迟值寄存器

//选择

EPwm2Regs.DCFCTL.bit.EDGEFILTSEL = 1;//数字滤波器(P.No.1984)

// DCAEVT2 = DCAH HI (将随着比较器输出变为 HI)>>>用于 epmwA

EPwm2Regs.DCTRIPSEL.bit.dCBHCOMPSEL = DC_TRIPIN4;

EPwm2Regs.TZDCSEL.bit.DCBEVT2 = TZ_DCBH_HI;

EPwm2Regs.DCBCTL.bit.EVT2CSEL = DC_EVT2;// DCAEVT2 = DCAEVT2 (未滤波)

EPwm2Regs.DCBCTL.bit.EVT2FRCSYNCSEL = DC_EVT_ASYNC;//获取异步路径

EPwm2Regs.TZSEL.bit.DCBEVT2 = 1;

EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_LO;// EPWM1B 将变为高电平

//启用 TZ 中断

EPwm2Regs.TZEINT.bit.CBC = 1;

EPwm1Regs.TZCLR.bit.INT = 1;

EDIS;

}

__interrupt void adcA1ISR (void)

{

//

//将最新结果添加到缓冲区中

// ADCRESULT0是 SOC0的结果寄存器

V_out = AdcaResultRegs.ADCRESULT0*3.3/4095;

V_IN = AdccResultRegs.ADCRESULT0*3.3/4095;

V1 = AdccResultRegs.ADCRESULT0*3.3/4095*30;//数字表单

// DACAL 值随负载电流而变化

Cmpss2Regs.DACHVALS.bit.DACVAL = 2500;// CMPSS DACVAL

EPwm2Regs.TBPRD =(a + b);

//清除中断标志

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1;

//检查是否发生了溢出

if (1 == AdcaRegs.ADCINTOVF.bit.ADCINT1)

{

AdcaRegs.ADCINTOVFCLR.bit.ADCINT1 = 1;//清除 INT1溢出标志

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1;//清除 INT1标志

}

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;//确认中断

}

void CMPSSInit (void){

EALLOW;

///CMP2_H、用于 IL 电流检测

Cmpss2Regs.COMPCTL.bit.COMPDACE = 1;启用//Comparator/DAC

Cmpss2Regs.COMPCTL.bit.ASYNCHEN = 0;//不馈入或门

Cmpss2Regs.COMPHYSCTL.bit.COMPHYS = 1;

//// 滤波器功能

Cmpss2Regs.CTRIPHFILCTL.bit.SAMPWIN = 4;

Cmpss2Regs.CTRIPHFILCTL.bit.THRESH = 2;

Cmpss2Regs.CTRIPHFILCLKCTL.bit.CLKPRESCALE = 0;

Cmpss2Regs.CTRIPHFILCTL.bit.FILINIT = 1;

Cmpss2Regs.COMPSTSCLR.bit.HLATCHCLR = 1;

//// CTRIPOUTH = CLBX-BAR 输入

Cmpss2Regs.COMPCTL.bit.CTRIPOUTHSEL = 2;//同步比较器输出驱动 CTRIPOUTH

Cmpss2Regs.COMPCTL.bit.CTRIPHSEL = 2;//同步比较器输出驱动 CTRIPH

Cmpss2Regs.COMPCTL.bit.COMPHINV = 0;//比较器的输出未反相

Cmpss2Regs.COMPCTL.bit.COMPHSOURCE = 0;//内部 DAC 驱动的比较器的反相输入

//// 选择 DACVAL 源。

Cmpss2Regs.COMPDACCTL.bit.SWLOADSEL = 0;//DACxVALA 在 SYSCLK 上从 DACxVALS 更新

Cmpss2Regs.COMPDACCTL.bit.DACSOURCE = 0;//DACHVALA 从 DACHVALS 更新

EDIS;

}

void XBARInit (void){

EALLOW;

//配置 EPWM_XBAR (页号1029)

//TRIP4、用于 OVP/OVP TRIG

EPwmXbarRegs.TRIP4MUX0TO15CFG.bit.MUX2 = 0;//配置为 CMPSS2 CTRIPH

EPwmXbarRegs.TRIP4MUXENABLE .bit.MUX2 = 1;// Trip4 ePWM XBAR 多路复用器使能

//编写下面的代码行以查看 CMPSS 值

//配置 OUTPUT_XBAR3 GPIO5

//配置 OUTPUTXBAR3 = CMP2_H

OutputXbarRegs.OUTPUT1MUX0TO15CFG.bit.MUX2 = 0;//CMPSS2.CTRIPOUTH

OutputXbarRegs.OUTPUT1MUXENABLE。bit.MUX2 = 1;

// OutputXbarRegs.OUTPUT6MUX0TO15CFG.bit.MUX2 = 0;// CMPSS2.CTRIPOUTH

// OutputXbarRegs.OUTPUT6MUXENABLE.bit.MUX2 = 1;

EDIS;

}