主题中讨论的其他器件: C2000WARE

您好!

我正在使用 TMS320F280041微控制器实现对相移全桥转换器的控制。

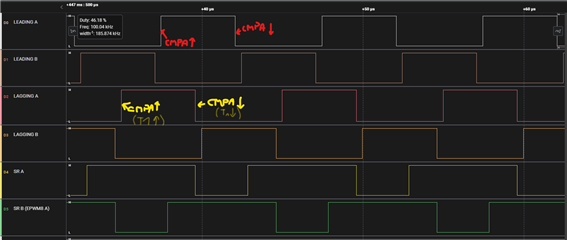

电源通过 EPWM1-EPWM4相移进行控制。 EPWM1和 EPWM4设置为向上向下模式并链接(EPWM1同步输出用作 EPWM4同步输入、并通过 TBPHS 寄存器进行相位控制)。 频率为100kHz、占空比为50%。 相移在范围(1;0、5)内(epwm1滞后于 epwm4)。 控制环路频率为10kHz

这对我来说很好。

但是、我将尝试使用 EPWM1和 EPM4输出关闭和开启事件在 EPM7上实现同步整流器控制、与本主题中所述的类似:

https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1158329/tms320f280048-q1-how-to-obtain-sr-waveforms-by-monitoring-other-epwm-channels-on-and-off-edges?tisearch=e2e-sitesearch&keymatch=synchronize%252520rectifier#

我使用 T1事件来实现该目的、其理念是:

EPWM1:向上向下计数模式、在 CMPA 向上计数时开启、在 CMPA 向下计数时关闭

EPWM4:上升/下降模式、在 CMPA 上升时开启、关闭 CMPA 下降、相对于 EPWM1的相移、CMPB 等于 CMPA 对于 EPWM7是同步输出

EPWM7:向上/向下模式、默认设置为 EPWM1、但从 EPWM4同步输入用作 T1事件、因此输出由 T1和 CMPA 事件控制

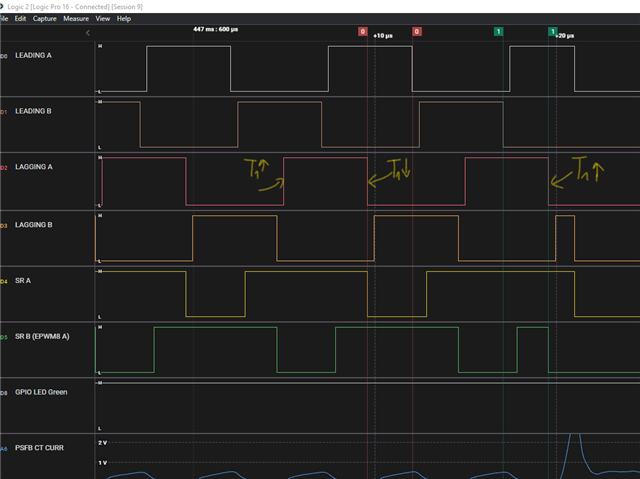

正如我看到的、T1的逻辑与相移有关。 当相移大于0.75时、我用于控制 EPWM7输出的事件为 T1D、低于0.75、此事件将更改为 T1U。

因此、我必须为 EPWM7更改动作限定器的"动态"配置。

问题是、当我在相移为0.75时更改此配置(我是通过检查 TBPRD 和 TBPHS 寄存器及其关系来进行此操作)、那么有时候看起来好像太早了-

动作限定器配置已更改、因此它会对 T1U 而不是 T1D 做出反应、这会破坏所需的 PWM 波形。

您能帮助我调查并理解这个问题吗? 如果需要、我稍后会用代码和图像更新此主题。

我想继续使用 T1事件方法、因为我正在使用带有 CMPSS 的数字比较模块进行保护