大家好、

客户有问题需要您的帮助:

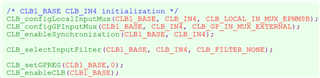

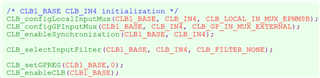

我们在应用中使用 CLB 模块、其目的是通过 CLB 将 EPWM8B 配置为特定的 IO 引脚、IO 引脚本身无法配置为 ePWM 端口。 配置如下:EPWM8B AQ 模块的输出用作 CLB_IN4的输入、CLB output6的输出通过 CLBoutputxbar 配置为 IO 引脚。 结果表明、与原始 epwm8B 模块相比、CLB 模块之后的驱动波形具有固定的延迟(23ns)。 有什么方法可以解决它吗? 谢谢!

此致、

本

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

客户有问题需要您的帮助:

我们在应用中使用 CLB 模块、其目的是通过 CLB 将 EPWM8B 配置为特定的 IO 引脚、IO 引脚本身无法配置为 ePWM 端口。 配置如下:EPWM8B AQ 模块的输出用作 CLB_IN4的输入、CLB output6的输出通过 CLBoutputxbar 配置为 IO 引脚。 结果表明、与原始 epwm8B 模块相比、CLB 模块之后的驱动波形具有固定的延迟(23ns)。 有什么方法可以解决它吗? 谢谢!

此致、

本