什么是将一个输出从一个 CLB 逻辑块传递到另一个 CLB 逻辑块的输入的正确方法?

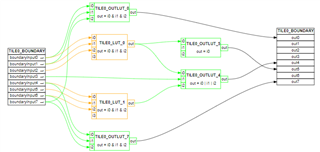

示例... 下面是 CLB 逻辑块(TILE0);想要使用 out0和 out 7作为另一个逻辑块(TILE1)的输入。

TILE0:

字段1:

对于 TILE1的边界输入、在 syscfg 中有如下配置:

目的是使用 TILE0 out0作为 TILE1 i4的输入、并使用 TILE0 out7作为 TILE1 i5的输入。

使用 Simulink.. 在"硬件实现/目标硬件资源"中、按照如下所示设置 CLB TILE1输入:

将 IN4和 iN5设置为 GPREG 输入0;这是否正确?

这些参数。 TILE0 out0和 out7似乎没有传递给 TILE1 i4和 i5。 我通过将 i4或 i5发送到 TILE1 out4或 Out5来测试此性能(out4和 Out5发送到输出 X-BAR、其中信号分配给 GPIO)