您好!

我们一直在使用提供的预编译库、并取得了一些成功、但现在我们要将该功能转移到一个更复杂的设计中。设计中存在资源限制、需要更好地理解源代码、以确保它使用正确的资源并正确配置时钟。

我们的设计现在要求 CLB 时钟为100 MHz、PWM 时钟为200 MHz、此外、我们的新设计使用 EPWM1、我们不确定需要更改什么内容才能正确支持该功能。

1) 1)在 PM_Bissc_setupPeriph 中的示例设计中、EPWM1A 连接到 CLB3和 CLB4的 CLB_IN0、6和7。 在示例中、从不配置 EPWM1。 该信号预期的行为是什么? 它有什么作用?

2) 2)在 PM_Bissc_configureCLBLength 中的示例设计中、CLB4_BASE 中的 CLB_ADDR_COUNTER_1_MATCH1被强制为200。 这个值是多少? 如果 CLB 的时钟频率为100MHz、此值是否应更改为100?

3) 3)当我们将25传递到 PM_Bissc_setFreq 中时、我们会得到一个4 MHz BiSS-C 输出时钟、文档和注释会指示这应该是2 MHz。 时钟频率 = SYSCLK/(4*BISC_FREQ_DIVIDER)。 我们的 SYSCLK 为200 MHz、看起来我们现在的差异是2倍?

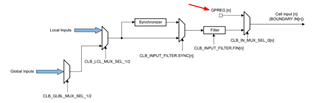

4) 4)我确定这个问题很愚蠢、时钟显然来自正确的引脚、引脚配置为连接 EPWM4A 和4B。 完成设置后、我们使用跳闸区强制输出为高电平、但我在代码中不明白 CLB 是如何与 ePWM 通信的。 EPWM4已启用、但未配置跳匣区域以外的区段。 CLB 如何控制 ePWM? 它们是如何进行物理连接的、即哪些 CLB 输出连接到 ePWM 输入?

谢谢!

珍妮弗