主题中讨论的其他器件: TMS320F28379S、 C2000WARE

您好!

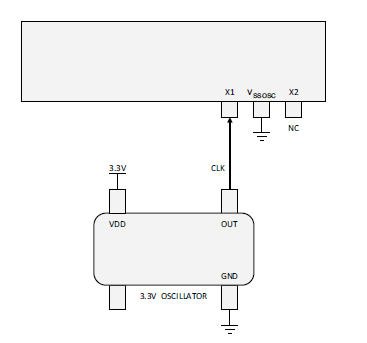

我有一个定制电路板、并且使用的是 TMS320F28379D。 当我编写 到闪存中时、运行正常。 然而、当我对电路板进行下电上电时、它似乎卡住、要等待 CLK (外部单端20MHz 振荡器)。 如果我使用 CCS 重新编程、它同样可以正常工作、但在下电上电时会卡住。

问题:

- MCU 在进行下电上电时卡滞。

- 我另一块采用 TMS320F28379S 的电路板、它不存在此问题。

- 如果我使用回流站加热 MCU、则不会出现此问题。 当系统冷却时、从下电上电启动所需的时间越来越长。 (3s、7s、20s、...、从不启动)。

有什么建议如何对此进行进一步调试、或者可能是什么问题? 我已经验证了以下内容:

- 外部 CLK

- MCU VDD、VDDIO 等。

- 复位引脚

- 引导模式引脚(GPIO72和 GPIO84)均被拉至高电平

非常感谢。