您好、TI 支持团队:

我已查看 以下 TI 文档

- C2000 F28P65x 系列 LaunchPad 开发套件

- TMS320F28P65x 实时微控制器、技术参考手册

- F28P65X 控制卡

我想请您 支持 几点。

根据我的理解、ESC EtherCAT 在 F28P65中运行:请您确认吗?

此外、我发现 EtherCAT 电气原理图有四个选项:请参阅后续选项。

选项1

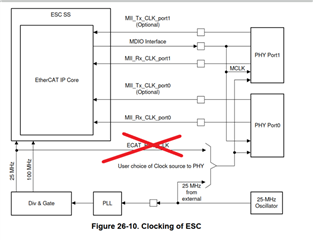

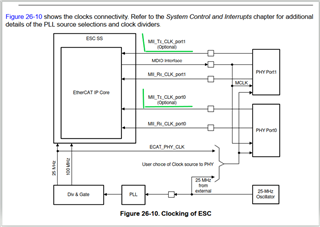

一个振荡器为 ESC 和 PHY 器件提供时钟、如下图所示。

选项2

一个振荡器为 ESC 提供时钟。

ESC 通过 GPIO154为 PHY 器件提供时钟、如下图所示。

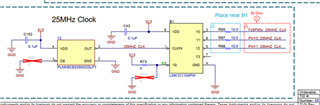

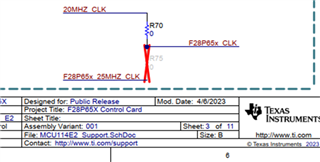

选项3

一个用于 EtherCAT PHY 的振荡器

一个用于 DSP 的振荡器

EtherCAT PHY

CPU 振荡器

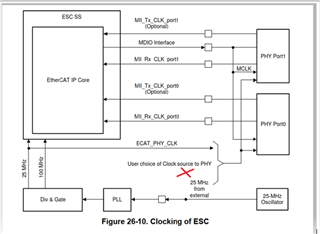

备选案文4

根据我的理解、用户手册未介绍此配置:请查看"问题"部分。

问题

假设我的逻辑板工作在电磁恶劣的环境中,您能推荐最佳的 EtherCAT 电路图吗?

关于 PCB 的布局,假设我们不想通过一个长网共享高频时钟信号,您还能建议最佳的电气图吗?

F28P65外设手册中、没有说明电气原理图中选项3:我是否正确?中显示的时钟生成或分配。 如果是,为什么?

根据"选项4"中显示的配置,请说明:

- MII_Tx_CLK_port1和 MII_Tx_CLK_port0的特性

- 这两个可选连接对时钟生成有何影响? 我的意思是红网上的时钟仍然是必要的吗?

非常感谢您的支持、

埃托尔