Other Parts Discussed in Thread: DP83640, TMS320F28388D

主题中讨论的其他器件:DP83640、

您好!

我们有一个 TMS320F28388D controlCARD (具有使用 MII 接口的板载 PHY)、一个带 TMS320F28388D 的定制 PCB 和一个带 RMII 接口的 TI DP83640 PHY。 我无法使后者正常工作、例如使用 ethernet_ex4_ptp_basic_master。 您能帮助我对 RMII 进行必要的更改并调试它不工作的原因吗?

我所做的:

- 首先、我在 controlCARD 上运行了示例"Ethernet_ex4_ptp_BASIC_MASTER"。 我只需在 cm_common_config_C28x 项目中定义宏"以太网"。 正如预期的那样、我每秒可以在 Wireshark 中看到 PTP 消息。

- 然后、我修改了 RMII 定制硬件的引脚:

//

//为以太网配置 GPIO。

//

//

// MDIO 信号

//

GPIO_setPinConfig (GPIO_105_ENET_MDIO_CLK); // PHY:MDC

GPIO_setPinConfig (GPIO_106_ENET_MDIO_DATA); // PHY:MDIO

//

//仅将其用于 RMII 模式

GPIO_setPinConfig (GPIO_73_ENET_RMII_CLK); //PHY:X1

//

//RMII 信号

//

GPIO_setPinConfig (GPIO_75_ENET_MII_TX_DATA0); //PHY:TXD_0

GPIO_setPinConfig (GPIO_122_ENET_MII_TX_DATA1); //PHY:TXD_1

GPIO_setPinConfig (GPIO_118_ENET_MII_TX_EN); //PHY:TX_EN

GPIO_setPinConfig (GPIO_114_ENET_MII_RX_DATA0); //PHY:RXD_0

GPIO_setPinConfig (GPIO_115_ENET_MII_RX_DATA1); //PHY:RXD_1

GPIO_setPinConfig (GPIO_113_ENET_MII_RX_ERR); //PHY:RX_ERR

GPIO_setPinConfig (GPIO_112_ENET_MII_RX_DV); //PHY:CRS/CRS_DV - 此外、我必须定义 USE_20MHz_XTAL、因为这是我们的定制板具有的功能。

- 最后、我更改了以太网_ex4_ptp_basic_master 中的此行

initInterfaceConfig.phyMode = Ethernet_SS_PHY_INTF_SEL_RMII;

并添加了

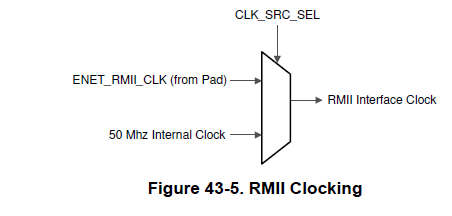

initInterfaceConfig.clockSel = Ethernet_SS_CLK_SRC_internal;

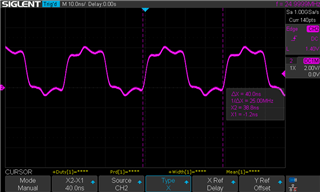

通过 SMI、我可以验证是否协商了100Mbit 全双工链路(有效链路标志变为高电平)。 我还可以测量 TX_EN、TXD_0、TXD_1 (示例预期每秒一次)和 RMII_CLK/X0上的活动。 但是、唉、Wireshark 中看不到任何内容。

将代码从 MII 迁移到 RMII 时、我是否错过了一些事情?

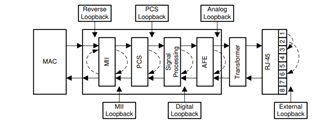

可以使用 EMAC 的任何寄存器来调试问题吗?

我们检查了 PHY 的所有搭接引脚、并通过 SMI 验证了配置(RMII 模式、RMII 从时钟模式)。

如果有任何提示,我们将不胜感激。

此致、Nils