主题中讨论的其他器件:C2000WARE、 SysConfig、

e2e.ti.com/.../2023_2D00_10_2D00_05-12_2D00_18_2D00_19.mp4

请尽快解决问题。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

e2e.ti.com/.../2023_2D00_10_2D00_05-12_2D00_18_2D00_19.mp4

请尽快解决问题。

尊敬的所有人:

我们安装了最新的 CCS 版本:Code Composer Studio 12.5.0

您在尝试导入其他实验(例如本实验的 controlCARD 版本或其他 F280013x 培训实验)时是否遇到相同的问题? 还是只有这个 ADC 培训实验会给您带来问题?

对于所有具有相同问题的问题、请尽早解决、因为我们的项目因上次 week.e2e.ti.com/.../2023_2D00_10_2D00_06-10_2D00_57_2D00_56.mp4中的此问题而出现延迟

您好!

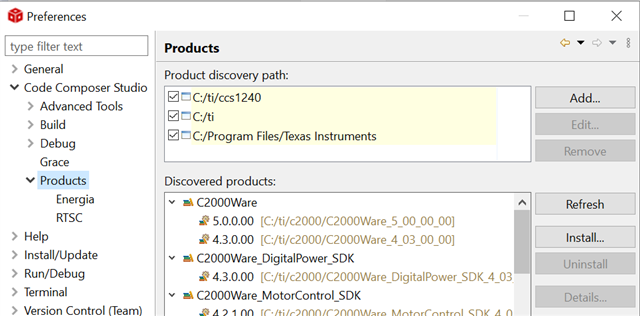

CCS 需要将 C2000Ware 检测为产品。 您可以通过依次单击"CCS"->"Windows"->"Preferences"->"Products"

此时会打开一个列出所有产品的窗口、请参阅以下快照

如果 C2000Ware 未列出、请尝试通过此链接 https://www.ti.com/tool/download/C2000WARE 安装 C2000Ware。

然后导入项目。

此致

西达尔特

由于未列出 C2000Ware、因此请尝试通过此链接 https://www.ti.com/tool/download/C2000WARE 安装 C2000Ware 、然后导入工程。

此致

西达尔特

//############################################################################# // // FILE: lab_main.c // // TITLE: adc lab // // C2K ACADEMY URL: dev.ti.com/.../node // //! \addtogroup academy_lab_list //! <h1> Using Analog Subsystems Lab - Sysconfig </h1> //! //! The objective of this lab exercise is to become familiar with the //! programming and operation of the on-chip analog-to-digital converter (ADC). //! The microcontroller (MCU) will be setup to sample a single ADC input //! channel at a prescribed sampling rate and store the conversion result in a //! circular memory buffer. In the second part of this lab exercise, the //! digital-to-analog converter (DAC) will be explored. //! //! \b External \b Connections \n //! - Refer to Academy Lab instruction for exact pin for your device/board //! //! \b Watch \b Variables \n //! - None. //! //############################################################################# // $Copyright: // Copyright (C) 2022 Texas Instruments Incorporated - http://www.ti.com // // Redistribution and use in source and binary forms, with or without // modification, are permitted provided that the following conditions // are met: // // Redistributions of source code must retain the above copyright // notice, this list of conditions and the following disclaimer. // // Redistributions in binary form must reproduce the above copyright // notice, this list of conditions and the following disclaimer in the // documentation and/or other materials provided with the // distribution. // // Neither the name of Texas Instruments Incorporated nor the names of // its contributors may be used to endorse or promote products derived // from this software without specific prior written permission. // // THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS // "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT // LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR // A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT // OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, // SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT // LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, // DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY // THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT // (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE // OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. // $ //############################################################################# // // Included Files // #include "board.h" // // Global variables and definitions // #define ADC_BUF_LEN 50 uint16_t DEBUG_TOGGLE = 1; // Used for real-time mode uint16_t AdcBuf[ADC_BUF_LEN]; // ADC buffer allocation #ifdef DACB_BASE uint16_t DacOutput; uint16_t DacOffset; uint16_t SINE_ENABLE = 0; // quadrature look-up table: contains 4 quadrants of sinusoid data points #define SINE_PTS 25 int QuadratureTable[SINE_PTS] = { 0x0000, // [0] 0.0 0x1FD4, // [1] 14.4 0x3DA9, // [2] 28.8 0x579E, // [3] 43.2 0x6C12, // [4] 57.6 0x79BB, // [5] 72.0 0x7FBE, // [6] 86.4 0x7DBA, // [7] 100.8 0x73D0, // [8] 115.2 0x629F, // [9] 129.6 0x4B3B, // [10] 144.0 0x2F1E, // [11] 158.4 0x100A, // [12] 172.8 0xEFF6, // [13] 187.2 0xD0E2, // [14] 201.6 0xB4C5, // [15] 216.0 0x9D61, // [16] 230.4 0x8C30, // [17] 244.8 0x8246, // [18] 259.2 0x8042, // [19] 273.6 0x8645, // [20] 288.0 0x93EE, // [21] 302.4 0xA862, // [22] 316.8 0xC257, // [23] 331.2 0xE02C // [24] 345.6 }; #endif // // Function Declarations // __interrupt void INT_myADCA_1_ISR(void); // // Main // void main(void) { // CPU Initialization Device_init(); Interrupt_initModule(); Interrupt_initVectorTable(); // Configure the GPIOs/ADC/PWM through SysConfig generated files Board_init(); // Enable global interrupts and real-time debug EINT; ERTM; // Main Loop while(1){} } interrupt void INT_myADCA_1_ISR(void) { static uint16_t *AdcBufPtr = AdcBuf; uint16_t LED_count = 0; // Read the ADC Result *AdcBufPtr++ = ADC_readResult(myADCA_RESULT_BASE, myADCA_SOC0); // Brute Force the circular buffer if (AdcBufPtr == (AdcBuf + ADC_BUF_LEN)) { AdcBufPtr = AdcBuf; } // Toggle the pin if(DEBUG_TOGGLE == 1) { GPIO_togglePin(myGPIOToggle); } if(LED_count++ > 25000) // Toggle slowly to see the LED blink { GPIO_togglePin(myBoardLED0_GPIO); // Toggle the pin LED_count = 0; // Reset the counter } #ifdef DACB_BASE // Write to DAC-B to create input to ADC-A0 static uint16_t iQuadratureTable = 0; // Quadrature table index if(SINE_ENABLE == 1) { DacOutput = DacOffset + ((QuadratureTable[iQuadratureTable++] ^ 0x8000) >> 5); } else { DacOutput = DacOffset; } if(iQuadratureTable > (SINE_PTS - 1)) // Wrap the index { iQuadratureTable = 0; } DAC_setShadowValue(myDACB_BASE, DacOutput); #endif Interrupt_clearACKGroup(INT_myADCA_1_INTERRUPT_ACK_GROUP); ADC_clearInterruptStatus(myADCA_BASE, ADC_INT_NUMBER1); } // End of ADC ISR // // End of File //

//############################################################################# // // FILE: device.h // // TITLE: Device setup for examples. // //############################################################################# // // // $Copyright: // Copyright (C) 2023 Texas Instruments Incorporated - http://www.ti.com/ // // Redistribution and use in source and binary forms, with or without // modification, are permitted provided that the following conditions // are met: // // Redistributions of source code must retain the above copyright // notice, this list of conditions and the following disclaimer. // // Redistributions in binary form must reproduce the above copyright // notice, this list of conditions and the following disclaimer in the // documentation and/or other materials provided with the // distribution. // // Neither the name of Texas Instruments Incorporated nor the names of // its contributors may be used to endorse or promote products derived // from this software without specific prior written permission. // // THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS // "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT // LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR // A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT // OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, // SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT // LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, // DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY // THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT // (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE // OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. // $ //############################################################################# #ifndef __DEVICE_H__ #define __DEVICE_H__ #ifdef __cplusplus extern "C" { #endif // // Included Files // #include "driverlib.h" // // Check for invalid compile flags // #if defined(__TMS320C28XX_FPU64__) #error "Invalid FPU Configuration" #endif #if defined(__TMS320C28XX_TMU1__) #error "Invalid TMU Configuration" #endif //***************************************************************************** // // Defines for pin numbers // //***************************************************************************** #ifdef _LAUNCHXL_F2800137 // // LaunchPad // // // LEDs // #define DEVICE_GPIO_PIN_LED1 20U // GPIO number for LED4 #define DEVICE_GPIO_PIN_LED2 22U // GPIO number for LED5 #define DEVICE_GPIO_CFG_LED1 GPIO_20_GPIO20 // "pinConfig" for LED4 #define DEVICE_GPIO_CFG_LED2 GPIO_22_GPIO22 // "pinConfig" for LED5 // // CANA // #define DEVICE_GPIO_PIN_CANRXA 5U // GPIO number for CANA RX #define DEVICE_GPIO_PIN_CANTXA 4U // GPIO number for CANA TX #define DEVICE_GPIO_CFG_CANRXA GPIO_5_CANA_RX // "pinConfig" for CANA RX #define DEVICE_GPIO_CFG_CANTXA GPIO_4_CANA_TX // "pinConfig" for CANA TX // // SCI for USB-to-UART adapter on XDS110 chip // #define DEVICE_GPIO_PIN_SCIRXDA 28U // GPIO number for SCIA RX #define DEVICE_GPIO_PIN_SCITXDA 29U // GPIO number for SCIA TX #define DEVICE_GPIO_CFG_SCIRXDA GPIO_28_SCIA_RX // "pinConfig" for SCIA RX #define DEVICE_GPIO_CFG_SCITXDA GPIO_29_SCIA_TX // "pinConfig" for SCIA TX // // I2CA // #define DEVICE_GPIO_PIN_SDAA 32U // GPIO number for I2C SDAA #define DEVICE_GPIO_PIN_SCLA 33U // GPIO number for I2C SCLA #define DEVICE_GPIO_CFG_SDAA GPIO_32_I2CA_SDA // "pinConfig" for I2C SDAA #define DEVICE_GPIO_CFG_SCLA GPIO_33_I2CA_SCL // "pinConfig" for I2C SCLA #define DEVICE_GPIO_PIN_SDAA_2 19U // GPIO number for I2C SDAA #define DEVICE_GPIO_PIN_SCLA_2 18U // GPIO number for I2C SCLA #define DEVICE_GPIO_CFG_SDAA_2 GPIO_19_I2CA_SDA // "pinConfig" for I2C SDAA #define DEVICE_GPIO_CFG_SCLA_2 GPIO_18_I2CA_SCL // "pinConfig" for I2C SCLA #define DEVICE_GPIO_PIN_SDAB 28U // GPIO number for I2C SDAA #define DEVICE_GPIO_PIN_SCLB 29U // GPIO number for I2C SCLA #define DEVICE_GPIO_CFG_SDAB GPIO_28_I2CB_SDA // "pinConfig" for I2C SDAA #define DEVICE_GPIO_CFG_SCLB GPIO_29_I2CB_SCL // "pinConfig" for I2C SCLA // // SPIA // #define DEVICE_GPIO_PIN_SPICLKA 9U // GPIO number for SPI CLKA #define DEVICE_GPIO_PIN_SPISIMOA 8U // GPIO number for SPI SIMOA #define DEVICE_GPIO_PIN_SPISOMIA 17U // GPIO number for SPI SOMIA #define DEVICE_GPIO_PIN_SPISTEA 5U // GPIO number for SPI STEA #define DEVICE_GPIO_CFG_SPICLKA GPIO_9_SPIA_CLK // "pinConfig" for SPI CLKA #define DEVICE_GPIO_CFG_SPISIMOA GPIO_8_SPIA_SIMO // "pinConfig" for SPI SIMOA #define DEVICE_GPIO_CFG_SPISOMIA GPIO_17_SPIA_SOMI // "pinConfig" for SPI SOMIA #define DEVICE_GPIO_CFG_SPISTEA GPIO_5_SPIA_STE // "pinConfig" for SPI STEA // // eQEP1 // #define DEVICE_GPIO_PIN_EQEP1A 40U // GPIO number for EQEP 1A #define DEVICE_GPIO_PIN_EQEP1B 41U // GPIO number for EQEP 1B #define DEVICE_GPIO_PIN_EQEP1I 39U // GPIO number for EQEP 1I #define DEVICE_GPIO_CFG_EQEP1A GPIO_40_EQEP1_A // "pinConfig" for EQEP 1A #define DEVICE_GPIO_CFG_EQEP1B GPIO_41_EQEP1_B // "pinConfig" for EQEP 1B #define DEVICE_GPIO_CFG_EQEP1I GPIO_39_EQEP1_INDEX // "pinConfig" for EQEP 1I #else // // ControlCARD // // // LEDs // #define DEVICE_GPIO_PIN_LED1 24U // GPIO number for LED1 #define DEVICE_GPIO_PIN_LED2 39U // GPIO number for LED2 #define DEVICE_GPIO_CFG_LED1 GPIO_24_GPIO24 // "pinConfig" for LED1 #define DEVICE_GPIO_CFG_LED2 GPIO_39_GPIO39 // "pinConfig" for LED2 // // CANA // #define DEVICE_GPIO_PIN_CANTXA 32U // GPIO number for CANTXA #define DEVICE_GPIO_PIN_CANRXA 33U // GPIO number for CANRXA #define DEVICE_GPIO_CFG_CANRXA GPIO_33_CANA_RX // "pinConfig" for CANA RX #define DEVICE_GPIO_CFG_CANTXA GPIO_32_CANA_TX // "pinConfig" for CANA TX // // SCI for USB-to-UART adapter on FTDI chip // #define DEVICE_GPIO_PIN_SCIRXDA 28U // GPIO number for SCI RX #define DEVICE_GPIO_PIN_SCITXDA 29U // GPIO number for SCI TX #define DEVICE_GPIO_CFG_SCIRXDA GPIO_28_SCIA_RX // "pinConfig" for SCI RX #define DEVICE_GPIO_CFG_SCITXDA GPIO_29_SCIA_TX // "pinConfig" for SCI TX // // I2C // #define DEVICE_GPIO_PIN_SDAA 32U // GPIO number for I2C SDAA #define DEVICE_GPIO_PIN_SCLA 33U // GPIO number for I2C SCLA #define DEVICE_GPIO_CFG_SDAA GPIO_32_I2CA_SDA // "pinConfig" for I2C SDAA #define DEVICE_GPIO_CFG_SCLA GPIO_33_I2CA_SCL // "pinConfig" for I2C SCLA //I2CB GPIO pins #define DEVICE_GPIO_PIN_SDAB 2 #define DEVICE_GPIO_PIN_SCLB 3 #define DEVICE_GPIO_CFG_SDAB GPIO_2_I2CB_SDA #define DEVICE_GPIO_CFG_SCLB GPIO_3_I2CB_SCL #endif //***************************************************************************** // // Defines related to clock configuration // //***************************************************************************** // // To use XTAL as the clock source, uncomment #define USE_PLL_SRC_XTAL, // and comment the #define USE_PLL_SRC_INTOSC // //#define USE_PLL_SRC_XTAL #define USE_PLL_SRC_INTOSC // // To use CPU frequency as 100MHZ, uncomment #define CPU_FRQ_100MHZ, // and comment the #define CPU_FRQ_120MHZ // //#define CPU_FRQ_100MHZ #define CPU_FRQ_120MHZ #if defined(USE_PLL_SRC_XTAL) // // 20MHz XTAL on controlCARD is used as the PLL source. // For use with SysCtl_getClock(). // #define DEVICE_OSCSRC_FREQ 20000000U #if defined(CPU_FRQ_100MHZ) // // Define to pass to SysCtl_setClock(). Will configure the clock as follows: // PLLSYSCLK = 20MHz (XTAL_OSC) * 30 (IMULT) / (2 (REFDIV) * 3 (ODIV) * 1(SYSDIV)) // #define DEVICE_SETCLOCK_CFG (SYSCTL_OSCSRC_XTAL | SYSCTL_IMULT(30) | \ SYSCTL_REFDIV(2) | SYSCTL_ODIV(3) | \ SYSCTL_SYSDIV(1) | SYSCTL_PLL_ENABLE | \ SYSCTL_DCC_BASE_0) // // 100MHz SYSCLK frequency based on the above DEVICE_SETCLOCK_CFG. Update the // code below if a different clock configuration is used! // #define DEVICE_SYSCLK_FREQ ((DEVICE_OSCSRC_FREQ * 30) / (2 * 3 * 1)) #elif defined(CPU_FRQ_120MHZ) // // Define to pass to SysCtl_setClock(). Will configure the clock as follows: // PLLSYSCLK = 20MHz (XTAL_OSC) * 48 (IMULT) / (2 (REFDIV) * 4 (ODIV) * 1(SYSDIV)) // #define DEVICE_SETCLOCK_CFG (SYSCTL_OSCSRC_XTAL | SYSCTL_IMULT(48) | \ SYSCTL_REFDIV(2) | SYSCTL_ODIV(4) | \ SYSCTL_SYSDIV(1) | SYSCTL_PLL_ENABLE | \ SYSCTL_DCC_BASE_0) // // 120MHz SYSCLK frequency based on the above DEVICE_SETCLOCK_CFG. Update the // code below if a different clock configuration is used! // #define DEVICE_SYSCLK_FREQ ((DEVICE_OSCSRC_FREQ * 48) / (2 * 4 * 1)) #endif #elif defined(USE_PLL_SRC_INTOSC) // // 10MHz INTOSC on the device is used as the PLL source. // For use with SysCtl_getClock(). // #define DEVICE_OSCSRC_FREQ 10000000U #if defined(CPU_FRQ_100MHZ) // // Define to pass to SysCtl_setClock(). Will configure the clock as follows: // PLLSYSCLK = 10MHz (INT_OSC2) * 30 (IMULT) / (1 (REFDIV) * 3 (ODIV) * 1(SYSDIV)) // #define DEVICE_SETCLOCK_CFG (SYSCTL_OSCSRC_OSC2 | SYSCTL_IMULT(30) | \ SYSCTL_REFDIV(1) | SYSCTL_ODIV(3) | \ SYSCTL_SYSDIV(1) | SYSCTL_PLL_ENABLE | \ SYSCTL_DCC_BASE_0) // // 100MHz SYSCLK frequency based on the above DEVICE_SETCLOCK_CFG. Update the // code below if a different clock configuration is used! // #define DEVICE_SYSCLK_FREQ ((DEVICE_OSCSRC_FREQ * 30) / (1 * 3 * 1)) #elif defined(CPU_FRQ_120MHZ) // // Define to pass to SysCtl_setClock(). Will configure the clock as follows: // PLLSYSCLK = 10MHz (INT_OSC2) * 48 (IMULT) / (1 (REFDIV) * 4 (ODIV) * 1(SYSDIV)) // #define DEVICE_SETCLOCK_CFG (SYSCTL_OSCSRC_OSC2 | SYSCTL_IMULT(48) | \ SYSCTL_REFDIV(1) | SYSCTL_ODIV(4) | \ SYSCTL_SYSDIV(1) | SYSCTL_PLL_ENABLE | \ SYSCTL_DCC_BASE_0) // // 120MHz SYSCLK frequency based on the above DEVICE_SETCLOCK_CFG. Update the // code below if a different clock configuration is used! // #define DEVICE_SYSCLK_FREQ ((DEVICE_OSCSRC_FREQ * 48) / (1 * 4 * 1)) #endif #endif // // 30MHz (25MHz in case if DEVICE_SYSCLK_FREQ = 100MHz) LSPCLK frequency based on the above DEVICE_SYSCLK_FREQ and a default // low speed peripheral clock divider of 4. Update the code below if a // different LSPCLK divider is used! // #define DEVICE_LSPCLK_FREQ (DEVICE_SYSCLK_FREQ / 4) //***************************************************************************** // // Macro to call SysCtl_delay() to achieve a delay in microseconds. The macro // will convert the desired delay in microseconds to the count value expected // by the function. \b x is the number of microseconds to delay. // //***************************************************************************** #define DEVICE_DELAY_US(x) SysCtl_delay(((((long double)(x)) / (1000000.0L / \ (long double)DEVICE_SYSCLK_FREQ)) - 9.0L) / 5.0L) //***************************************************************************** // // Defines, Globals, and Header Includes related to Flash Support // //***************************************************************************** #ifdef _FLASH #include <stddef.h> #ifndef CMDTOOL extern uint16_t RamfuncsLoadStart; extern uint16_t RamfuncsLoadEnd; extern uint16_t RamfuncsLoadSize; extern uint16_t RamfuncsRunStart; extern uint16_t RamfuncsRunEnd; extern uint16_t RamfuncsRunSize; #endif #endif #define DEVICE_FLASH_WAITSTATES 2 //***************************************************************************** // // Function Prototypes // //***************************************************************************** //***************************************************************************** // //! \addtogroup device_api //! @{ // //***************************************************************************** //***************************************************************************** // //! @brief Function to initialize the device. Primarily initializes system //! control to aknown state by disabling the watchdog, setting up the //! SYSCLKOUT frequency, and enabling the clocks to the peripherals. //! //! \param None. //! \return None. // //***************************************************************************** extern void Device_init(void); //***************************************************************************** //! //! //! @brief Function to turn on all peripherals, enabling reads and writes to the //! peripherals' registers. //! //! Note that to reduce power, unused peripherals should be disabled. //! //! @param None //! @return None // //***************************************************************************** extern void Device_enableAllPeripherals(void); //***************************************************************************** //! //! //! @brief Function to disable pin locks on GPIOs. //! //! @param None //! @return None // //***************************************************************************** extern void Device_initGPIO(void); //***************************************************************************** //! //! @brief Error handling function to be called when an ASSERT is violated //! //! @param *filename File name in which the error has occurred //! @param line Line number within the file //! @return None // //***************************************************************************** extern void __error__(const char *filename, uint32_t line); //***************************************************************************** // // Close the Doxygen group. //! @} // //***************************************************************************** #ifdef __cplusplus } #endif #endif // __DEVICE_H__

您好!

更改 SysConfig 配置不会更新 lab_main.c 或 device.h 文件。 它会生成文件 board.c 和 board.h、您可在其中查看在 SysConfig 中完成的更改。

请访问以下链接

https://software-dl.ti.com/C2000/docs/software_guide/c2000_sysconfig.html

视频- https://www.ti.com/video/6304748751001

此致

西达尔特

尊敬的 Siddharth:

请查看所附的 J17、即 TENVI 问题、为什么每次程序进入错误循环/起作用?

e2e.ti.com/.../TENVI_5F00_issue.mp4

请检查并解决此问题。

/* * Copyright (c) 2020 Texas Instruments Incorporated - http://www.ti.com * All rights reserved. * * Redistribution and use in source and binary forms, with or without * modification, are permitted provided that the following conditions * are met: * * * Redistributions of source code must retain the above copyright * notice, this list of conditions and the following disclaimer. * * * Redistributions in binary form must reproduce the above copyright * notice, this list of conditions and the following disclaimer in the * documentation and/or other materials provided with the distribution. * * * Neither the name of Texas Instruments Incorporated nor the names of * its contributors may be used to endorse or promote products derived * from this software without specific prior written permission. * * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, * THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR * PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR * CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, * EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, * PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; * OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, * WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR * OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, * EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. * */ #include "board.h" //***************************************************************************** // // Board Configurations // Initializes the rest of the modules. // Call this function in your application if you wish to do all module // initialization. // If you wish to not use some of the initializations, instead of the // Board_init use the individual Module_inits // //***************************************************************************** void Board_init() { EALLOW; PinMux_init(); SYNC_init(); ASYSCTL_init(); ADC_init(); EPWM_init(); GPIO_init(); INTERRUPT_init(); EDIS; } //***************************************************************************** // // PINMUX Configurations // //***************************************************************************** void PinMux_init() { // // PinMux for modules assigned to CPU1 // // // ANALOG -> temp_ensor Pinmux // // Analog PinMux for A15/C7 GPIO_setPinConfig(GPIO_233_GPIO233); // AIO -> Analog mode selected GPIO_setAnalogMode(233, GPIO_ANALOG_ENABLED); // Analog PinMux for A18/C18, GPIO21 GPIO_setPinConfig(GPIO_21_GPIO21); // AGPIO -> Analog mode selected GPIO_setAnalogMode(21, GPIO_ANALOG_ENABLED); // Analog PinMux for C6, GPIO226 GPIO_setPinConfig(GPIO_226_GPIO226); // AGPIO -> Analog mode selected GPIO_setAnalogMode(226, GPIO_ANALOG_ENABLED); // // EPWM1 -> myEPWM0 Pinmux // GPIO_setPinConfig(myEPWM0_EPWMA_PIN_CONFIG); GPIO_setPadConfig(myEPWM0_EPWMA_GPIO, GPIO_PIN_TYPE_STD); GPIO_setQualificationMode(myEPWM0_EPWMA_GPIO, GPIO_QUAL_SYNC); GPIO_setPinConfig(myEPWM0_EPWMB_PIN_CONFIG); GPIO_setPadConfig(myEPWM0_EPWMB_GPIO, GPIO_PIN_TYPE_STD); GPIO_setQualificationMode(myEPWM0_EPWMB_GPIO, GPIO_QUAL_SYNC); // GPIO22 -> myBoardLED0_GPIO Pinmux GPIO_setPinConfig(GPIO_22_GPIO22); // GPIO37/TDO -> myGPIOHigh Pinmux GPIO_setPinConfig(GPIO_37_GPIO37); // GPIO23 -> myGPIOToggle Pinmux GPIO_setPinConfig(GPIO_23_GPIO23); } //***************************************************************************** // // ADC Configurations // //***************************************************************************** void ADC_init(){ myADCA_init(); } void myADCA_init(){ // // ADC Initialization: Write ADC configurations and power up the ADC // // Configures the ADC module's offset trim // ADC_setOffsetTrimAll(ADC_REFERENCE_INTERNAL,ADC_REFERENCE_3_3V); // // Configures the analog-to-digital converter module prescaler. // ADC_setPrescaler(myADCA_BASE, ADC_CLK_DIV_4_0); // // Sets the timing of the end-of-conversion pulse // ADC_setInterruptPulseMode(myADCA_BASE, ADC_PULSE_END_OF_CONV); // // Powers up the analog-to-digital converter core. // ADC_enableConverter(myADCA_BASE); // // Delay for 1ms to allow ADC time to power up // DEVICE_DELAY_US(5000); // // SOC Configuration: Setup ADC EPWM channel and trigger settings // // Disables SOC burst mode. // ADC_disableBurstMode(myADCA_BASE); // // Sets the priority mode of the SOCs. // ADC_setSOCPriority(myADCA_BASE, ADC_PRI_ALL_ROUND_ROBIN); // // Start of Conversion 0 Configuration // // // Configures a start-of-conversion (SOC) in the ADC and its interrupt SOC trigger. // SOC number : 0 // Trigger : ADC_TRIGGER_EPWM1_SOCA // Channel : ADC_CH_ADCIN18 // Sample Window : 20 SYSCLK cycles // Interrupt Trigger: ADC_INT_SOC_TRIGGER_NONE // ADC_setupSOC(myADCA_BASE, ADC_SOC_NUMBER0, ADC_TRIGGER_EPWM1_SOCA, ADC_CH_ADCIN18, 20U); ADC_setInterruptSOCTrigger(myADCA_BASE, ADC_SOC_NUMBER0, ADC_INT_SOC_TRIGGER_NONE); // // ADC Interrupt 1 Configuration // Source : ADC_SOC_NUMBER0 // Interrupt Source: enabled // Continuous Mode : disabled // // ADC_setInterruptSource(myADCA_BASE, ADC_INT_NUMBER1, ADC_SOC_NUMBER0); ADC_clearInterruptStatus(myADCA_BASE, ADC_INT_NUMBER1); ADC_disableContinuousMode(myADCA_BASE, ADC_INT_NUMBER1); ADC_enableInterrupt(myADCA_BASE, ADC_INT_NUMBER1); } //***************************************************************************** // // ASYSCTL Configurations // //***************************************************************************** void ASYSCTL_init(){ // // asysctl initialization // // Disables the temperature sensor output to the ADC. // ASysCtl_disableTemperatureSensor(); // // Set the analog voltage reference selection to internal. // ASysCtl_setAnalogReferenceInternal( ASYSCTL_VREFHI ); // // Set the internal analog voltage reference selection to 1.65V. // ASysCtl_setAnalogReference1P65( ASYSCTL_VREFHI ); } //***************************************************************************** // // EPWM Configurations // //***************************************************************************** void EPWM_init(){ EPWM_setClockPrescaler(myEPWM0_BASE, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_1); EPWM_setTimeBasePeriod(myEPWM0_BASE, 1999); EPWM_setTimeBaseCounter(myEPWM0_BASE, 0); EPWM_setTimeBaseCounterMode(myEPWM0_BASE, EPWM_COUNTER_MODE_UP); EPWM_disablePhaseShiftLoad(myEPWM0_BASE); EPWM_setPhaseShift(myEPWM0_BASE, 0); EPWM_setCounterCompareValue(myEPWM0_BASE, EPWM_COUNTER_COMPARE_A, 0); EPWM_setCounterCompareShadowLoadMode(myEPWM0_BASE, EPWM_COUNTER_COMPARE_A, EPWM_COMP_LOAD_ON_CNTR_ZERO); EPWM_setCounterCompareValue(myEPWM0_BASE, EPWM_COUNTER_COMPARE_B, 0); EPWM_setCounterCompareShadowLoadMode(myEPWM0_BASE, EPWM_COUNTER_COMPARE_B, EPWM_COMP_LOAD_ON_CNTR_ZERO); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPB); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB); EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPB); EPWM_setRisingEdgeDelayCountShadowLoadMode(myEPWM0_BASE, EPWM_RED_LOAD_ON_CNTR_ZERO); EPWM_setFallingEdgeDelayCountShadowLoadMode(myEPWM0_BASE, EPWM_FED_LOAD_ON_CNTR_ZERO); EPWM_disableRisingEdgeDelayCountShadowLoadMode(myEPWM0_BASE); EPWM_disableFallingEdgeDelayCountShadowLoadMode(myEPWM0_BASE); EPWM_enableInterrupt(myEPWM0_BASE); EPWM_enableADCTrigger(myEPWM0_BASE, EPWM_SOC_A); EPWM_setADCTriggerSource(myEPWM0_BASE, EPWM_SOC_A, EPWM_SOC_TBCTR_PERIOD); EPWM_setADCTriggerEventPrescale(myEPWM0_BASE, EPWM_SOC_A, 1); } //***************************************************************************** // // GPIO Configurations // //***************************************************************************** void GPIO_init(){ myBoardLED0_GPIO_init(); myGPIOHigh_init(); myGPIOToggle_init(); } void myBoardLED0_GPIO_init(){ GPIO_setPadConfig(myBoardLED0_GPIO, GPIO_PIN_TYPE_STD); GPIO_setQualificationMode(myBoardLED0_GPIO, GPIO_QUAL_SYNC); GPIO_setDirectionMode(myBoardLED0_GPIO, GPIO_DIR_MODE_OUT); } void myGPIOHigh_init(){ GPIO_writePin(myGPIOHigh, 1); GPIO_setPadConfig(myGPIOHigh, GPIO_PIN_TYPE_STD | GPIO_PIN_TYPE_PULLUP); GPIO_setQualificationMode(myGPIOHigh, GPIO_QUAL_SYNC); GPIO_setDirectionMode(myGPIOHigh, GPIO_DIR_MODE_OUT); } void myGPIOToggle_init(){ GPIO_writePin(myGPIOToggle, 1); GPIO_setPadConfig(myGPIOToggle, GPIO_PIN_TYPE_STD | GPIO_PIN_TYPE_PULLUP); GPIO_setQualificationMode(myGPIOToggle, GPIO_QUAL_SYNC); GPIO_setDirectionMode(myGPIOToggle, GPIO_DIR_MODE_OUT); } //***************************************************************************** // // INTERRUPT Configurations // //***************************************************************************** void INTERRUPT_init(){ // Interrupt Setings for INT_myADCA_1 Interrupt_register(INT_myADCA_1, &INT_myADCA_1_ISR); Interrupt_disable(INT_myADCA_1); } //***************************************************************************** // // SYNC Scheme Configurations // //***************************************************************************** void SYNC_init(){ SysCtl_setSyncOutputConfig(SYSCTL_SYNC_OUT_SRC_EPWM1SYNCOUT); // // SOCA // SysCtl_enableExtADCSOCSource(0); // // SOCB // SysCtl_enableExtADCSOCSource(0); }

/* * Copyright (c) 2020 Texas Instruments Incorporated - http://www.ti.com * All rights reserved. * * Redistribution and use in source and binary forms, with or without * modification, are permitted provided that the following conditions * are met: * * * Redistributions of source code must retain the above copyright * notice, this list of conditions and the following disclaimer. * * * Redistributions in binary form must reproduce the above copyright * notice, this list of conditions and the following disclaimer in the * documentation and/or other materials provided with the distribution. * * * Neither the name of Texas Instruments Incorporated nor the names of * its contributors may be used to endorse or promote products derived * from this software without specific prior written permission. * * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, * THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR * PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR * CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, * EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, * PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; * OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, * WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR * OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, * EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. * */ #ifndef BOARD_H #define BOARD_H //***************************************************************************** // // If building with a C++ compiler, make all of the definitions in this header // have a C binding. // //***************************************************************************** #ifdef __cplusplus extern "C" { #endif // // Included Files // #include "driverlib.h" #include "device.h" //***************************************************************************** // // PinMux Configurations // //***************************************************************************** // // ANALOG -> temp_ensor Pinmux // // // EPWM1 -> myEPWM0 Pinmux // // // EPWM1_A - GPIO Settings // #define GPIO_PIN_EPWM1_A 0 #define myEPWM0_EPWMA_GPIO 0 #define myEPWM0_EPWMA_PIN_CONFIG GPIO_0_EPWM1_A // // EPWM1_B - GPIO Settings // #define GPIO_PIN_EPWM1_B 1 #define myEPWM0_EPWMB_GPIO 1 #define myEPWM0_EPWMB_PIN_CONFIG GPIO_1_EPWM1_B // // GPIO22 - GPIO Settings // #define myBoardLED0_GPIO_GPIO_PIN_CONFIG GPIO_22_GPIO22 // // GPIO37 - GPIO Settings // #define myGPIOHigh_GPIO_PIN_CONFIG GPIO_37_GPIO37 // // GPIO23 - GPIO Settings // #define myGPIOToggle_GPIO_PIN_CONFIG GPIO_23_GPIO23 //***************************************************************************** // // ADC Configurations // //***************************************************************************** #define myADCA_BASE ADCC_BASE #define myADCA_RESULT_BASE ADCCRESULT_BASE #define myADCA_SOC0 ADC_SOC_NUMBER0 #define myADCA_FORCE_SOC0 ADC_FORCE_SOC0 #define myADCA_SAMPLE_WINDOW_SOC0 166.66666666666669 #define myADCA_TRIGGER_SOURCE_SOC0 ADC_TRIGGER_EPWM1_SOCA #define myADCA_CHANNEL_SOC0 ADC_CH_ADCIN18 void myADCA_init(); //***************************************************************************** // // ASYSCTL Configurations // //***************************************************************************** //***************************************************************************** // // EPWM Configurations // //***************************************************************************** #define myEPWM0_BASE EPWM1_BASE #define myEPWM0_TBPRD 1999 #define myEPWM0_COUNTER_MODE EPWM_COUNTER_MODE_UP #define myEPWM0_TBPHS 0 #define myEPWM0_CMPA 0 #define myEPWM0_CMPB 0 #define myEPWM0_CMPC 0 #define myEPWM0_CMPD 0 #define myEPWM0_DBRED 0 #define myEPWM0_DBFED 0 #define myEPWM0_TZA_ACTION EPWM_TZ_ACTION_HIGH_Z #define myEPWM0_TZB_ACTION EPWM_TZ_ACTION_HIGH_Z #define myEPWM0_INTERRUPT_SOURCE EPWM_INT_TBCTR_DISABLED //***************************************************************************** // // GPIO Configurations // //***************************************************************************** #define myBoardLED0_GPIO 22 void myBoardLED0_GPIO_init(); #define myGPIOHigh 37 void myGPIOHigh_init(); #define myGPIOToggle 23 void myGPIOToggle_init(); //***************************************************************************** // // INTERRUPT Configurations // //***************************************************************************** // Interrupt Settings for INT_myADCA_1 #define INT_myADCA_1 INT_ADCC1 #define INT_myADCA_1_INTERRUPT_ACK_GROUP INTERRUPT_ACK_GROUP1 extern __interrupt void INT_myADCA_1_ISR(void); //***************************************************************************** // // SYNC Scheme Configurations // //***************************************************************************** //***************************************************************************** // // Board Configurations // //***************************************************************************** void Board_init(); void ADC_init(); void ASYSCTL_init(); void EPWM_init(); void GPIO_init(); void INTERRUPT_init(); void SYNC_init(); void PinMux_init(); //***************************************************************************** // // Mark the end of the C bindings section for C++ compilers. // //***************************************************************************** #ifdef __cplusplus } #endif #endif // end of BOARD_H definition

请解决上述视频问题。

请参阅下面的 GPIO.c 文件