尊敬的 Champ:

我想就我当前面临的问题征求您的意见。 我的应用使用两个 PWM 模块、PWM1和 PWM2。 相位在 PWM2上启用、PWM1作为 SYNCIN (主器件)。

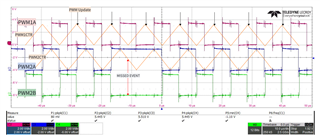

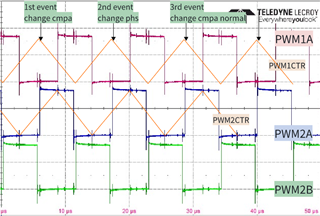

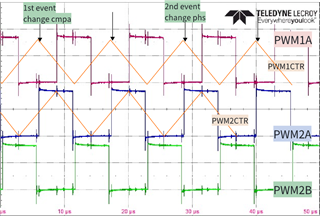

当相位在 CMPA 值附近缓慢下降时、就会出现问题。 我观察到 PWM2在一个周期内跳过。 根据我在此处找到的一些帖子、建议的解决方案是处理相位更新、方法是在一个周期内将 CMPA 值更改为小于 TBPHS、然后在下一个周期将 CMPA 改回正常值。

但是,这种方法(*)不能解决本例中的问题。 是否有需要添加的特定设置或处理程序?

我在这里附上了我的代码供您参考。

void PWM_init(void){

EPwm1Regs.TBPRD = pwm_prd;

EPwm1Regs.TBPHS.bit.TBPHS = 0; // PWM-1 serves as reference

EPwm1Regs.CMPA.bit.CMPA = pwm_cmpa;

EPwm1Regs.CMPB.bit.CMPB = 0;

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //change to sysclk

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Symmetrical mode

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm1Regs.EPWMSYNCOUTEN.bit.ZEROEN = 1;

EPwm1Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_DISABLE_ALL;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm1Regs.AQCTLA.bit.CAD = AQ_SET; // Active high

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CAD = AQ_CLEAR; // Active LOW

EPwm1Regs.AQCTLB.bit.CAU = AQ_SET;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // Enable Dead-band module

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Active Hi complementary

EPwm1Regs.DBFED.bit.DBFED = Deadtime;

EPwm1Regs.DBRED.bit.DBRED = Deadtime;

EPwm2Regs.TBPRD = pwm_prd;

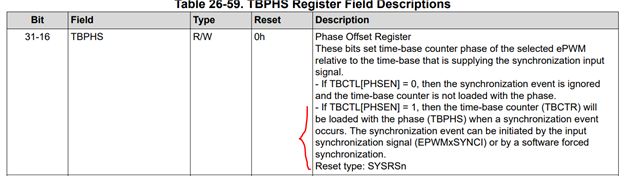

EPwm2Regs.TBPHS.bit.TBPHS = pwm_phs;

EPwm2Regs.CMPA.bit.CMPA = pwm_cmpa;

EPwm2Regs.CMPB.bit.CMPB = 0;

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm2Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_SYNCOUT_EPWM1;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_IMMEDIATE;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_IMMEDIATE;

// EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero

// EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero

EPwm2Regs.AQCTLA.bit.CAD = AQ_CLEAR; //Active LOW

EPwm2Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm2Regs.AQCTLB.bit.CAD = AQ_SET; //Active HIGH

EPwm2Regs.AQCTLB.bit.CAU = AQ_CLEAR;

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // Enable Dead-band module

EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Active Hi complementary

EPwm2Regs.DBFED.bit.DBFED = Deadtime;

EPwm2Regs.DBRED.bit.DBRED = Deadtime;

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE;

}

void phase_update(uint16_t phase)

{

static uint16_t temp;

temp = (uint16_t)(((uint32_t)phase* EPwm1Regs.TBPRD) / 180);

pwm_phs = temp;

update_request = 1;

}

void PWMUpdate(void)

{

if (skip_pwm_flag == 1) {

EPwm2Regs.TBPHS.bit.TBPHS = pwm_phs;

pwm_phs_prev = EPwm2Regs.TBPHS.bit.TBPHS;

skip_pwm_flag++;

} else if (skip_pwm_flag == 2) {

EPwm2Regs.CMPA.bit.CMPA = (EPwm2Regs.TBPRD >> 1);

skip_pwm_flag = 0;

}

if (update_request == 1) {

update_request = 0;

if (pwm_phs_prev > EPwm2Regs.CMPA.bit.CMPA && pwm_phs <= EPwm2Regs.CMPA.bit.CMPA) {

EPwm2Regs.CMPA.bit.CMPA = pwm_phs - 1;

skip_pwm_flag = 1;

} else {

EPwm2Regs.TBPHS.bit.TBPHS = pwm_phs;

pwm_phs_prev = EPwm2Regs.TBPHS.bit.TBPHS;

}

}

}

E2E 参考(*)

https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1163045/tms320f28069-epwm-miss-cycle-while-tbphs-change?tisearch=e2e-sitesearch&keymatch=tbphs%2525252525252520cmpa%2525252525252520pwm%2525252525252520missed#

https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1161072/tms320f28033-when-tbphs-load-value-is-less-than-cmpa-value-the-below-figure-will-the-aq-action-be-lost