您好、专家

我将为执行 SFRA 编写一个新代码、并按照 C2000 软件频率响应分析器(SFRA)库用户指南(修订版 A)(TI.com)中给出的步骤操作

调用 SFRA_F32_CONFIG 时、我遇到一些错误、无法解决。 我还没有完全编写完代码。 但觉得这种错误并不涉及到这一点。 亲切的帮助

错误是

第167章:你不会是你的!

第18章:我是你的女人

代码如下所示、请帮助

此致

阿诺普

#include "F28x_project.h"

#include "driverlib.h"

#include "device.h"

#include "sfra_F32.h"

#ifndef NULL

#define NULL ((void *) 0x0)

#endif

#define SFRA_ISR_FREQ 100e3

#define SFRA_FREQ_START 2

#define SFRA_FREQ_STEP_COMPLEX ((float32_t) 1.105)

#define SFRA_AM振 幅((float32_t) 0.005)

#define SFRA_FREQ_LENGTH 100

SFRA_F32 sfra1;

float32_t plantMagVect[SFRA_FREQ_LENGTH];

float32_t plantPhaseVect[SFRA_FREQ_LENGTH];

float32_t olMagVect[SFRA_FREQ_LENGTH];

float32_t olPhaseVect [SFRA_FREQ_LENGTH];

float32_t clMagVect[SFRA_FREQ_LENGTH];

float32_t clPhaseVect [SFRA_FREQ_LENGTH];

float32_t freqVect[SFRA_FREQ_length];

外部长 FPUsinTable[];

__interrupt void epwm1_ISR (void);

void PWM_Config (void);

空 main (void)

{

InitSysCtrl();

CpuSysRegs.PCLKCR2.bit.EPWM1=1;

InitEPwm1Gpio();

Dint;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EALLOW;

PieVectTable.EPWM1_INT =&epwm1_isr;

EDIS;

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC =0;

EDIS;

PWM_Config ();

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC =1;

EDIS;

IER |= M_INT3;

PieCtrlRegs.PIEIER3.bit.INTx1 = 1;

EINT;

ERTM;

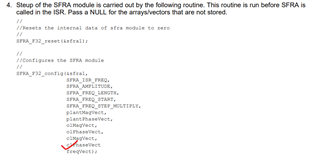

//将 SFRA 模块的内部数据复位为零

SFRA_F32_RESET (&sfra1);

//配置 SFRA 模块

SFRA_F32_CONFIG (&sfra1、

SFRA_ISR_FREQ、

SFRA_AM振 幅、

SFRA_FREQ_LENGTH、

SFRA_FREQ_START、

SFRA_FREQ_STEP_COMPLIT、

PlantMagVect、

PlantPhaseVect、

olMagVect、

olPhaseVect、

clMagVect、

clPhaseVect

频率 Vect、

1);

//将响应数组重置为全零

SFRA_F32_resetFreqRespArray (&sfra1);

//初始化频率响应数组

SFRA_F32_initFreqArrayWithLogSteps (&sfra1、

SFRA_FREQ_START、

SFRA_FREQ_STEP_SILIT);

for (;;)

{

}

}

__interrupt void epwm1_ISR (void)

{

EPwm1Regs.ETCLR.bit.INT = 1;

PieCtrlRegs.PIEACK.all = PIEACK_Group3;

}

空 PWM_Config ()

{

EPwm1Regs.TBPRD = 500;

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000;

EPwm1Regs.TBCTR = 0x0000;

EPwm1Regs.TBCTL.bit.CTRMODE = 2;

EPwm1Regs.TBCTL.bit.PHSEN = 0;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0;

EPwm1Regs.TBCTL.bit.CLKDIV = 0;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = 0;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = 0;

EPwm1Regs.CMPCTL.bit.LOADAMODE = 0;

EPwm1Regs.CMPCTL.bit.LOADBMODE = 0;

EPwm1Regs.CMPA.bit.CMPA = 150;

EPwm1Regs.AQCTLA.bit.CAU = 2;

EPwm1Regs.AQCTLA.bit.CAD = 1;

EPwm1Regs.DBCTL.all = 0x800B;

EPwm1Regs.DBRED.bit.DBRED = 50;

EPwm1Regs.DBFED.bit.DBFED = 50;

EPwm1Regs.ETSEL.bit.INTSEL = 1;

EPwm1Regs.ETSEL.bit.inten = 1;

EPwm1Regs.ETPS.bit.INTPRD = 1;

}