您好、TI 社区:

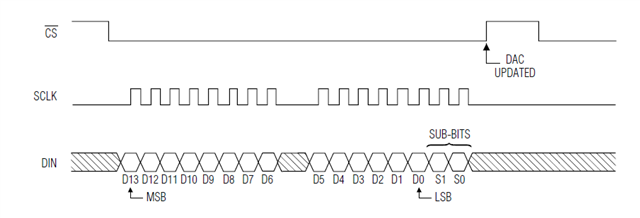

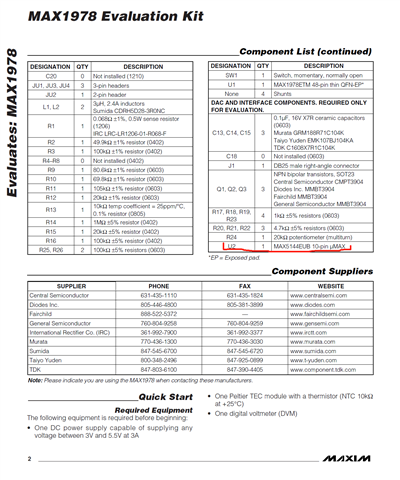

我在与 MAX1978器件的 SPI 通信过程中遇到间歇性错误。 通信在几个周期内正常运行、发送和接收预期数据(如0x88波形中的初始正确值所示)。 但是、在传输过程中有时会出现错误、导致无法正确接收或发送预期数据(波形中标有"错误")。

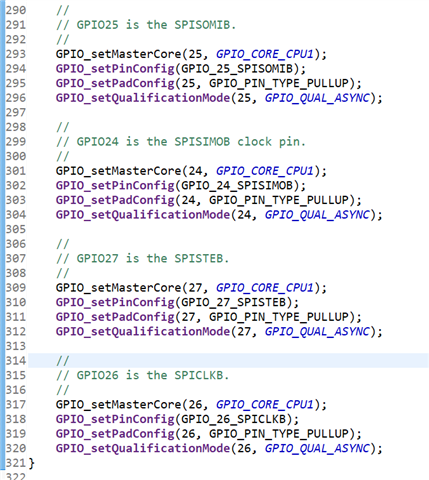

误差是零星的、不遵循明确的模式。 波形表明问题可能出在 SPI 配置或信号完整性、但我仔细检查了设置、它们符合器件的要求。 根据数据表规格配置时钟频率、SPI 模式和位顺序、并验证了硬件连接。

你们中是否有人遇到过类似问题、或者您是否对潜在原因有任何见解? 对于故障排除或要检查的特定领域的任何建议、我们将不胜感激。

感谢您的帮助。

此致、

戴内罗

e2e.ti.com/.../spi_5F00_ex3_5F00_external_5F00_loopback_5F00_fifo_5F00_interrupts.zipFull 代码已问世