主题中讨论的其他器件:UCC2895

我想使用 CMPSS 和 ePWM 模块实现逐周期跳闸。 其中 CMPIN1P 由外部馈送、并且与 DAC 值进行比较、以生成跳闸信号。 我将 CMPSS 的示例代码称为一次性跳闸、并对其进行了修改以适用于逐周期。

对于一次性跳闸代码

我为 CMPIN1P 使用了固定的直流值、当生成跳闸信号时、一次性跳闸强制 PWM 脉冲变为高电平。

当没有跳闸信号时、PWM 按预期正常。

对于逐周期跳闸

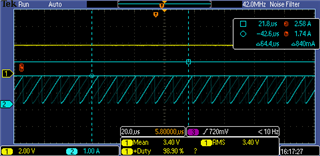

这里还用于生成的 CMPIN1P 跳闸的固定直流值和 PWM 脉冲变为高电平、而不是逐周期跳闸。

我在这里遗漏了一些配置吗?

规范如下:

void initEPWM (void)

{

EPwm8Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;//时钟与 SYSCLKOUT 的比率

EPwm8Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm8Regs.TBCTL.bit.PRDLD = TB_shadow;

EPwm8Regs.TBCTL.bit.PHSEN = TB_DISABLE;//启用相位加载

EPwm8Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO;//禁用相位同步

EPwm8Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;//递增/递减计数模式

EPwm8Regs.TBPHS.bit.TBPHS = 0x0000;//相位为120

EPwm8Regs.TBCTR = 0x0000;

//开关频率= 80kHz

EPwm8Regs.TBPRD = 1250;//设置 UCC2895时钟

//在零时设置影子寄存器加载

EPwm8Regs.CMPCTL.bit.SHDLBMODE = CC_HOLD;

EPwm8Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

// 1.667us 时钟脉冲宽度

EPwm8Regs.CMPB.bit.CMPB = 300;

//低电平有效配置

EPwm8Regs.AQCTLB.bit.CBU = AQ_SET;

EPwm8Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

//

//将 EPWM8B 配置为在 TZB 跳闸上输出高电平

//

EPwm8Regs.TZCTL.bit.TZB = TZ_FORCE_HI;

EPwm8Regs.TZSEL.bit.DCBEVT2 = 1;

EPwm8Regs.TZCLR.bit.CBCPULSE = 0;

EPwm8Regs.TZDCSEL.bit.dCBEVT2 = TZ_DCBH_HI;

EPwm8Regs.DCTRIPSEL.bit.dCBHCOMPSEL = 0xF;

EPwm8Regs.DCBHTRIPSEL.bit.TRIPINPUT4 = 1;

//将 DCB 路径配置为未过滤和异步

EPwm8Regs.DCBCTL.bit.EVT2SRCSEL = DC_EVT2;

EPwm8Regs.DCBCTL.bit.EVT2FRCSYNCSEL = DC_EVT_ASYNC;

//将 TRIP4配置为 CTRIP1H

EPwmXbarRegs.TRIP4MUX0TO15CFG.bit.MUX0 = 0;

//为输出启用 TRIP4多路复用器

EPwmXbarRegs.TRIP4MUXENABLE。bit.MUX0 = 1;

//清除跳闸标志

EPwm8Regs.TZCLR.bit.CBC = 1;

EPwm8Regs.TZCLR.bit.INT = 1;

EPwm8Regs.TZCBCCLR.bit.DCBEVT2 = 1;

EPwm8Regs.TZEINT.bit.CBC = 1;

void initCMPSS (void)

{

//

//启用 CMPSS 并将负输入信号配置为来自

// DAC

//

CMPSS_enableModule (CMPSS1_BASE);

CMPSS_CONFIGHighComparator (CMPSS1_BASE、CMPSS_INSRC_DAC);

//

//使用 VDDA 作为 DAC 的基准,并将 DAC 值设置为

//任意引用。

//

CMPSS_CONFIGDAC (CMPSS1_BASE、CMPSS_DACREF_VDDA | CMPSS_DACVAL_SYSCLK |

CMPSS_DACSRC_SHDW);

CMPSS_setDACValueHigh (CMPSS1_BASE、500);

//

//配置输出信号。 CTRIPH 和 CTRIPOUTH 将由以下人员馈送:

//异步比较器输出。

//

CMPSS_configOutputsHigh (CMPSS1_BASE、CMPSS_TRIP_ASYNC_COMP |

CMPSS_TRIPOUT_ASYNC_COMP);

//

//将输出 X-BAR 设置为 OUTPUTXBAR3上的输出 CTRIPOUTH

//

XBAR_setOutputMuxConfig (XBAR_OUTPUT3、XBAR_OUT_MUX00_CMPSS1_CTRIPOUTH);

XBAR_enableOutputMux (XBAR_OUTPUT3、XBAR_MUX00);

}