Other Parts Discussed in Thread: C2000WARE, TMS320F28386D, SYSCONFIG, TMS320F28388D, UNIFLASH

主题中讨论的其他器件: SysConfig、 TMS320F28388D、C2000WARE、 UNIFLASH

您好!

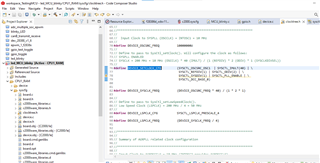

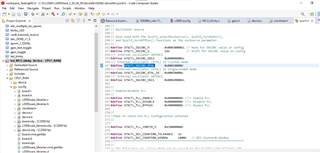

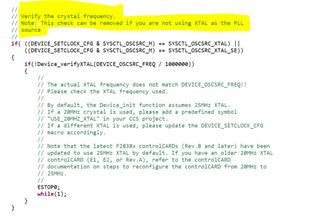

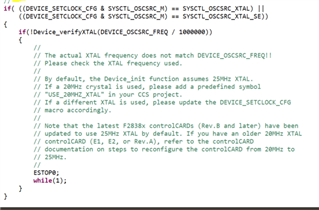

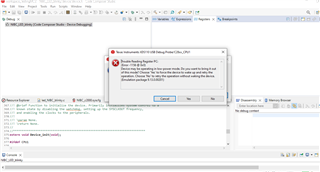

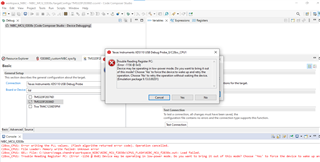

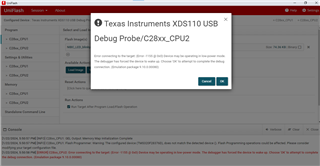

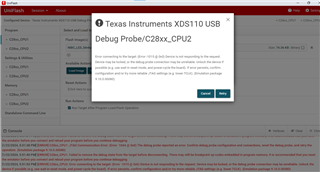

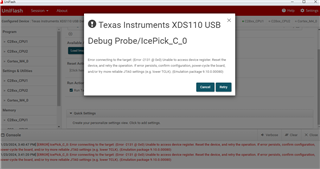

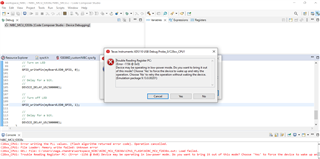

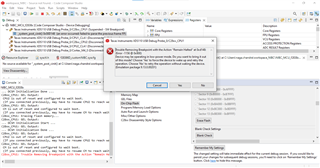

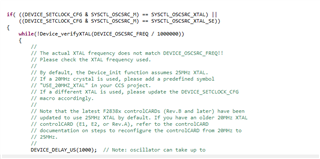

我使用的是具有外部振荡器的进化板(TMS320F28386D)、在调试期间我没有遇到任何问题。 但每当我 通过 SysConfig Tool 使用内部振荡器将板从 TMS320F28388D 切换到 TMS320F28386D 时,我的代码就会在 Device_init ()()暂挂,Kindle 让我知道如何解决这个问题。

当我尝试使用具有内部振荡器的 TMS320F28386D 进行调试时,代码将在 while ()和 Device_delay ()函数处挂起。 请告诉我为什么它挂在那里并分享评论

此致

班迪