您好:

我在使用 TMS320F28335系列芯片配置 HRPWM 时遇到了此类问题。 配置代码如下:

空

HRPWM6_Config (周期)

{

//

//使用 HRPWM 配置 ePWM6寄存器

// ePWM6A 通过在下降沿进行 MEP 控制来切换高/低电平

//

EPwm6Regs.TBCTL.bit.PRDLD = TB_immediate;//设置立即加载

EPwm6Regs.TBPRD =周期-1;

EPwm6Regs.CMPA.half.CMPA = 0;//仅通过 CMPAHR 设置占空比控制

EPwm6Regs.CMPA.half.CMPAHR =(255<< 8);//初始化 HRPWM 扩展

EPwm6Regs.TBPHS.all = 0;

EPwm6Regs.TBCTR = 0;

EPwm6Regs.TBCTL.bit.CTRMODE = TB_COUNT_DOWN;//向下计数模式

EPwm6Regs.TBCTL.bit.PHSEN = TB_DISABLE;// ePWM6是主控方

EPwm6Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE;

EPwm6Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm6Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm6Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm6Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm6Regs.CMPCTL.bit.SHDWAMODE = CC_影子;

EPwm6Regs.CMPCTL.bit.SHDWBMODE = CC_影子;

EPwm6Regs.AQCTLA.bit.ZRO = AQ_CLEAR;// PWM 切换高电平/低电平

EPwm6Regs.AQCTLA.bit.CAD = AQ_SET;

//EPwm6Regs.AQCTLB.bit.PRD = AQ_CLEAR;

//EPwm6Regs.AQCTLB.bit.CBU = AQ_CLEAR;

EALLOW;

EPwm6Regs.HRCNFG.all = 0x0;

EPwm6Regs.HRCNFG.bit.EDGMODE = HR_REP;//上升沿上的 MEP 控制

EPwm6Regs.HRCNFG.bit.CTLMODE = HR_CMP;

EPwm6Regs.HRCNFG.bit.HRLOAD = HR_CTR_ZERO;

EDIS;

}

在主函数中、我配置 SYSCLKOUT=PWM 150MHz 和 TBCLK=PWM、并且将15作为周期参数传递到 HRPWM6_Config (PERIOD)函数中、所以生成的150MHz 频率为15MHz。 现在我只想使用 CMPAHR 来控制占空比、所以将 CMPA 配置为0、而 CMPAHR=255、当 CTR = CAD 时、输出设置为 当 CTR = ZRO 时、输出很清晰、TMS320F28335的 MEP =150ps、因此生成的 PWM 的脉冲宽度应为255x150ps = 38.25、但我在示波器上看不到这样的 PWM 输出。 我想问一下、是否可以仅使用 CMPAHR 来控制 PWM 的占空比。 换句话说、在高精度模式下、CMPA 可以配置为0

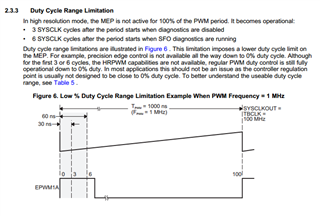

同时、为了避免 HRPWM 模式下的限制、将 COUNT 模式配置为 COUNT_DOWN、并使用 MEP 控制输出上升沿 REP、如下图所示:

根据本文档、可以通过在计数接近0时使用 MEP 配置上升沿 REP 来实现高精度 PWM 输出、因此我想知道是否可以将 CMPA 配置为0、换句话说、当 CMPA=0时、 HRPWM 模式的 MEP 技术是否仍然可用?

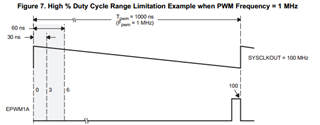

如果我想看到 MEP 边沿、那么使用示波器需要多大的带宽? 此外、我在配置期间发现、当 PWM 输出为30MHz 50%占空比时、GPIO 的 PWM 波形输出在示波器采样后接近正弦波(示波器带宽为200MHz)、 而且、当 PWM 频率降至15MHz 时、波形相对失真、如下图所示: