尊敬的先生:

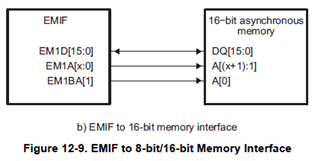

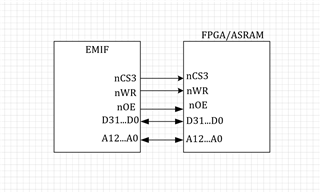

我们正在开发 基于 C2000 28384D 的控制器,并 使用 ASRC 模式 32位数据宽度配置的 EMIF 接口访问 FPGA 寄存器和存储器。

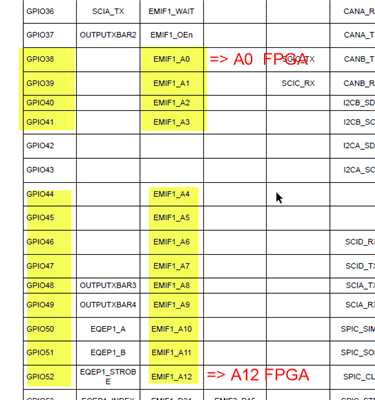

对于 地址 ,我们已连接 A0...A12 和 Data D31..D0。

访问 是 通过 CS3完成的 (例如、 地址范围从 0x300000开始...)。

我们正在看到 一些 改变的地址 , 这是不清楚的我们 . 如果我们 只能访问32位(使用 DMA/CPU ) ,我们预期 到下一个地址的访问 将是+1

(我们 正在探测 来自 A0...A12的地址总线)

例如

*(long *) 0x300000=0; // A0...A12 全0

*(long *) 0x300001=1; //A0 =1 、a1..a12 全部0

*(long *) 0x300002=2; //A0 =0 、A1 =1 、A2..A12=0

...

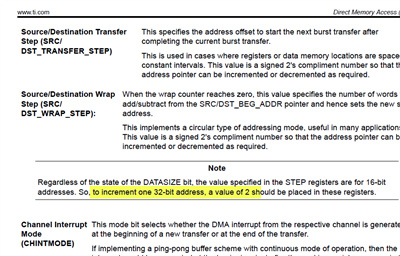

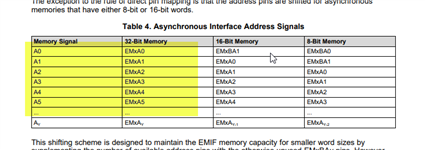

但 上述情况 不是 真的 (这是通过 DMA 在32位模式测试,并使用 CPU ) ,我们看到一些 移位 如下图所示 ,它看起来像, 为了访问 下一个地址 ,我们需要添加 +2

*(long *) 0x300000=0; // A0...A12 全0

*(long *) 0x300002=1; //A0 =1 、a1..a12 全部0

*(long *) 0x300004=2; //A0 =0 、A1 =1 、A2..A12=0

这是 它应该 工作的方式吗? 我假设 我 作为4Kx32位 存储器访问 FPGA 时 、每个 地址 将被+1间隔