主题中讨论的其他器件: SysConfig

您好!

我在定制电路板中有两个采用 JTAG 菊花链配置的 TMS320F28384D:

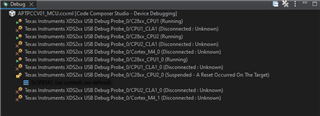

我将 CCS 12.5.0.00007和 CWARE 5.0.0.00与 XDS200调试探针一同使用。

直到昨天、我仍然能够毫无问题地对 RAM 或闪存中的两个器件进行编程和调试。

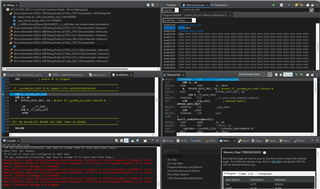

现在、我可以在两个 MCU 和所有内核中都在 RAM 中进行调试、但我不能在第二个 MCU 中的闪存中进行调试(考虑到链、它被称为 MCU1)。 在闪存中为第二个 MCU 的 CPU1 (CPU2也是如此)加载程序后、我总是得到以下错误:

"C28xx_CPU1_0:在0x82985处执行"Finish Auto Run"操作时、无法设置断点:(错误-1066 @ 0x82985)无法设置/清除请求的断点。 验证断点地址是否在有效的存储器中。 (仿真软件包9.13.0.00201)"

并且未正确加载程序。

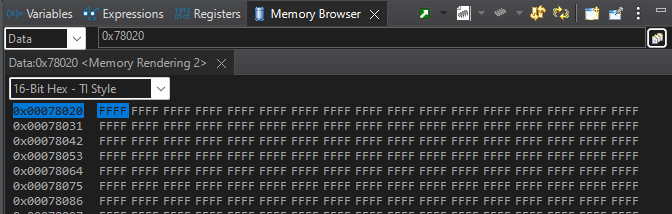

因此,如果我禁用"自动运行和启动选项"中的"在程序加载或重新启动上"选项 ,我没有得到错误,程序可以启动,它可以正常运行 (我说的正确、因为我正在使用示例"led ex1_c28x_dual_dblinky_cpu1" 和"led ex1_c28x_dual_dblinky_cpu2"、我可以看到闪烁、但对于我尝试添加的任何断点、我得到了错误:

"C28xx_CPU1_0:在0x829af 的操作"Remain Halted"中设置断点时出现问题:(ERROR -1066 @ 0x829AF)无法设置/清除请求的断点。 验证断点地址是否在有效的存储器中。 (仿真软件包9.13.0.00201) "

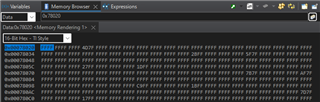

它停止、但我无法调试代码、只能在"Disassembly"窗口中进行调试。

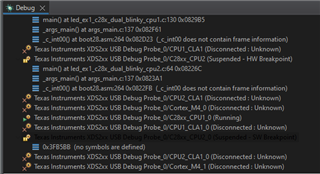

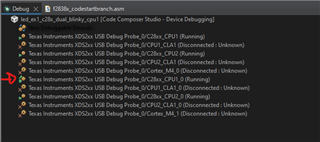

此外、现在我在第二个 MCU 的 CPU1的调试窗口上看到以下符号:

这意味着什么?

我已经尝试了一些关于清理工作区和目标配置文件的建议、但即使更改工作区也不起作用。

谢谢。此致、

法比奥