主题中讨论的其他器件:TIDM-DC-DC-BUCK、 PMP41081

您好!

我尝试控制一个3MHz 降压稳压器。 在此开关频率下、我可能会遇到哪些限制?

目标是使用峰值电流模式控制和大约300kHz 的目标交叉频率。

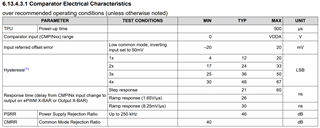

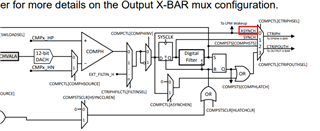

对于电流反馈、我想当电感电流达到电压控制阈值时、使用高速比较器向 MCU 发送一个标志。 这是因为采样率为3.92MSPS、此采样率不够快、不足以跟踪电感器纹波。 您认为这是可以实现的吗?

C2000能否接受电流环路的中断并仍保持控制?

除峰值电流模式控制外、您还使用了哪些其他控制方案? 是否有一种控制方案能够使2000年的亮点比其他方案更突出?

您可能有哪些其他建议可以实现这一点?