主题中讨论的其他器件:C2000WARE

尊敬的 专家:

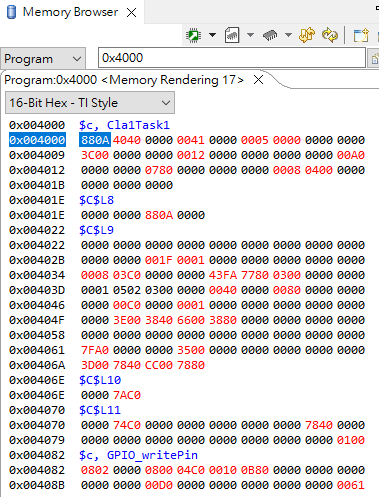

我有一个 TMS320F28P65X controlCARD。 我正在测试 cla_ex4_pwm_control 的示例并将其构建在 CPU1_FALSH 中。 一切都很正常、但当我 将 Cla1Prog 从 RAMLS0分配 给 RAMLS8_CLA 或 RAMLS9_CLA 时、CLA 不工作。 跟踪 SW 后、我发现 board.c 中的 memcpy 函数不能正常工作。 会有很多日期丢失。 你可以帮助去询问什么是问题?

MEMORY

{

BEGIN : origin = 0x080000, length = 0x000002 // Update the codestart location as needed

BOOT_RSVD : origin = 0x000002, length = 0x0001AF /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x0001B1, length = 0x00024F

RAMM1 : origin = 0x000400, length = 0x000400

RAMD0 : origin = 0x00C000, length = 0x002000

RAMD1 : origin = 0x00E000, length = 0x002000

RAMD2 : origin = 0x01A000, length = 0x002000 // Can be mapped to either CPU1 or CPU2. When configured to CPU2, use the address 0x8000. User should comment/uncomment based on core selection

RAMD3 : origin = 0x01C000, length = 0x002000 // Can be mapped to either CPU1 or CPU2. When configured to CPU2, use the address 0xA000. User should comment/uncomment based on core selection

RAMD4 : origin = 0x01E000, length = 0x002000 // Can be mapped to either CPU1 or CPU2. When configured to CPU2, use the address 0xC000. User should comment/uncomment based on core selection

RAMD5 : origin = 0x020000, length = 0x002000 // Can be mapped to either CPU1 or CPU2. When configured to CPU2, use the address 0xE000. User should comment/uncomment based on core selection

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

//RAMLS8 : origin = 0x022000, length = 0x002000 // When configured as CLA program use the address 0x4000

//RAMLS9 : origin = 0x024000, length = 0x002000 // When configured as CLA program use the address 0x6000

RAMLS8_CLA : origin = 0x004000, length = 0x002000 // Use only if configured as CLA program memory

RAMLS9_CLA : origin = 0x006000, length = 0x002000 // Use only if configured as CLA program memory

RAMGS0 : origin = 0x010000, length = 0x002000

RAMGS1 : origin = 0x012000, length = 0x002000

RAMGS2 : origin = 0x014000, length = 0x002000

RAMGS3 : origin = 0x016000, length = 0x002000

RAMGS4 : origin = 0x018000, length = 0x002000

/* Flash Banks (128 sectors each) */

FLASH_BANK0 : origin = 0x080002, length = 0x1FFFE // Can be mapped to either CPU1 or CPU2. User should comment/uncomment based on core selection

FLASH_BANK1 : origin = 0x0A0000, length = 0x20000 // Can be mapped to either CPU1 or CPU2. User should comment/uncomment based on core selection

FLASH_BANK2 : origin = 0x0C0000, length = 0x20000 // Can be mapped to either CPU1 or CPU2. User should comment/uncomment based on core selection

// FLASH_BANK3 : origin = 0x0E0000, length = 0x20000 // Can be mapped to either CPU1 or CPU2. User should comment/uncomment based on core selection

// FLASH_BANK4 : origin = 0x100000, length = 0x20000 // Can be mapped to either CPU1 or CPU2. User should comment/uncomment based on core selection

CPU1TOCPU2RAM : origin = 0x03A000, length = 0x000400

CPU2TOCPU1RAM : origin = 0x03B000, length = 0x000400

CLATOCPURAM : origin = 0x001480, length = 0x000080

CPUTOCLARAM : origin = 0x001500, length = 0x000080

CLATODMARAM : origin = 0x001680, length = 0x000080

DMATOCLARAM : origin = 0x001700, length = 0x000080

CANA_MSG_RAM : origin = 0x049000, length = 0x000800

CANB_MSG_RAM : origin = 0x04B000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

codestart : > BEGIN

.text : >> FLASH_BANK0 | FLASH_BANK1, ALIGN(8)

.cinit : > FLASH_BANK0, ALIGN(8)

.switch : > FLASH_BANK0, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

#if defined(__TI_EABI__)

.bss : > RAMLS5

.bss:output : > RAMLS3

.init_array : > FLASH_BANK0, ALIGN(8)

.const : > FLASH_BANK0, ALIGN(8)

.data : > RAMLS5

.sysmem : > RAMLS4

#else

.pinit : > FLASH_BANK0, ALIGN(8)

.ebss : >> RAMLS5 | RAMLS6

.econst : > FLASH_BANK0, ALIGN(8)

.esysmem : > RAMLS5

#endif

ramgs0 : > RAMGS0, type=NOINIT

ramgs1 : > RAMGS1, type=NOINIT

MSGRAM_CPU1_TO_CPU2 > CPU1TOCPU2RAM, type=NOINIT

MSGRAM_CPU2_TO_CPU1 > CPU2TOCPU1RAM, type=NOINIT

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASH_BANK0,

RUN = RAMLS4,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASH_BANK0,

RUN = RAMLS4,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

/* CLA specific sections */

#if defined(__TI_EABI__)

/* CLA specific sections */

Cla1Prog : LOAD = FLASH_BANK0,

RUN = RAMLS8_CLA,//RAMLS8_CLA,//RAMLS0,

LOAD_START(Cla1ProgLoadStart),

RUN_START(Cla1ProgRunStart),

LOAD_SIZE(Cla1ProgLoadSize),

ALIGN(4)

#else

/* CLA specific sections */

Cla1Prog : LOAD = FLASH_BANK0,

RUN = RAMLS8_CLA,//RAMLS8_CLA,//RAMLS0,

LOAD_START(_Cla1ProgLoadStart),

RUN_START(_Cla1ProgRunStart),

LOAD_SIZE(_Cla1ProgLoadSize),

ALIGN(4)

#endif

Cla1ToCpuMsgRAM : > CLATOCPURAM

CpuToCla1MsgRAM : > CPUTOCLARAM

.scratchpad : > RAMLS1

.bss_cla : > RAMLS1

Cla1DataRam : > RAMLS2

cla_shared : > RAMLS1

CLADataLS1 : > RAMLS1

#if defined(__TI_EABI__)

.const_cla : LOAD = FLASH_BANK0,

RUN = RAMLS1,

RUN_START(Cla1ConstRunStart),

LOAD_START(Cla1ConstLoadStart),

LOAD_SIZE(Cla1ConstLoadSize),

ALIGN(4)

#else

.const_cla : LOAD = FLASH_BANK0,

RUN = RAMLS1,

RUN_START(_Cla1ConstRunStart),

LOAD_START(_Cla1ConstLoadStart),

LOAD_SIZE(_Cla1ConstLoadSize),

ALIGN(4)

#endif

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

/**

* These arguments were used when this file was generated. They will be automatically applied on subsequent loads

* via the GUI or CLI. Run CLI with '--help' for additional information on how to override these arguments.

* @cliArgs --device "F28P65x" --package "256ZEJ" --part "F28P65x_256ZEJ" --context "CPU1" --product "C2000WARE@5.01.00.00"

* @versions {"tool":"1.18.0+3266"}

*/

/**

* Import the modules used in this configuration.

*/

const cla = scripting.addModule("/driverlib/cla.js", {}, false);

const cla1 = cla.addInstance();

const memcfg = scripting.addModule("/driverlib/memcfg.js");

/**

* Write custom configuration values to the imported modules.

*/

cla1.$name = "myCLA0";

cla1.cpuint_CLA_TASK_1 = false;

cla1.cpuint_CLA_TASK_2 = false;

cla1.cpuint_CLA_TASK_3 = false;

cla1.cpuint_CLA_TASK_4 = false;

cla1.cpuint_CLA_TASK_5 = false;

cla1.cpuint_CLA_TASK_6 = false;

cla1.cpuint_CLA_TASK_7 = false;

cla1.cpuint_CLA_TASK_8 = false;

cla1.trigger_CLA_TASK_1 = "CLA_TRIGGER_EPWM4INT";

memcfg.config_MEMCFG_SECT_LS0 = "CLA_prog";

memcfg.config_MEMCFG_SECT_LS1 = "CLA_data";

memcfg.config_MEMCFG_SECT_LS2 = "CLA_data";

memcfg.init_MEMCFG_SECT_MSGCPUTOCLA1 = true;

memcfg.init_MEMCFG_SECT_MSGCLA1TOCPU = true;

memcfg.config_MEMCFG_SECT_LS8 = "CLA_prog";

memcfg.config_MEMCFG_SECT_LS9 = "CLA_prog";

Cla1Prog 是 RAMLS0。

Cla1Prog 是 RAMLS8_CLA。