主题中讨论的其他器件:C2000WARE

大家好、

客户有问题需要您的帮助:

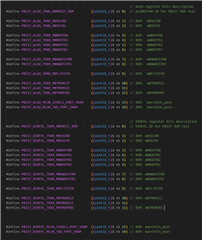

文件路径为 C:\ti\c2000\C2000Ware_5_01_00_00\libraries\boot_rom\f28002x\rev0\rom_sources\F28002x_rom\bootROM\include\cpu1brom_pbist.h

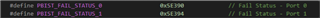

如下图所示、定义了两个寄存器

因此、我们需要查明、

1.为什么使用 port0和 port1,它是否与 PBIST 需要测试的存储体有关?

2.在什么情况下 port0 port1会失败?

此致、

本