大家好、

我在28379d 器件上为我的应用生成了 Intel hex 文件。

链接器命令文件中的段段落如下所示:

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHB | FLASHC PAGE = 0, ALIGN(8)

.text : >> FLASHB | FLASHC | FLASHD | FLASHE PAGE = 0, ALIGN(8)

codestart : > APP_START PAGE = 0, ALIGN(8)

/* Allocate uninitalized data sections: */

.stack : > RAMM1 PAGE = 1

.switch : > FLASHB PAGE = 0, ALIGN(8)

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

#if defined(__TI_EABI__)

.init_array : > FLASHB | FLASHC, PAGE = 0, ALIGN(8)

.bss : > RAMLS4LS5, PAGE = 1

.bss:output : > RAMLS4LS5, PAGE = 1

.bss:cio : > RAMLS4LS5, PAGE = 1

.data : > RAMLS4LS5, PAGE = 1

.sysmem : > RAMLS4LS5, PAGE = 1

/* Initalized sections go in Flash */

.const : > FLASHF, PAGE = 0, ALIGN(8)

#else

.pinit : > FLASHB, PAGE = 0, ALIGN(8)

.ebss : >> RAMLS4LS5 | RAMGS0 | RAMGS1, PAGE = 1

.esysmem : > RAMLS4LS5, PAGE = 1

.cio : > RAMLS4LS5, PAGE = 1

/* Initalized sections go in Flash */

.econst : >> FLASHF PAGE = 0, ALIGN(8)

#endif

// Filter_RegsFile : > RAMGS0, PAGE = 1

// SHARERAMGS0 : > RAMGS0, PAGE = 1

// SHARERAMGS1 : > RAMGS1, PAGE = 1

// SHARERAMGS2 : > RAMGS2, PAGE = 1

// ramgs0 : > RAMGS0, PAGE = 1

// ramgs1 : > RAMGS1, PAGE = 1

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 15009000

#if defined(__TI_EABI__)

GROUP

{

.TI.ramfunc

{

-l sfra_f32_tmu_eabi.lib

}

ramfuncs

isrcodefuncs

} LOAD = FLASHD,

RUN = RAMLS0LS1LS2LS3,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

PAGE = 0, ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASHD,

RUN = RAMLS0LS1LS2LS3,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(8)

#endif

#else

ramfuncs : LOAD = FLASHD,

RUN = RAMLS0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(8)

#endif

#endif

...

}

可以看出、align (8)用于闪存中分配的每个外观。

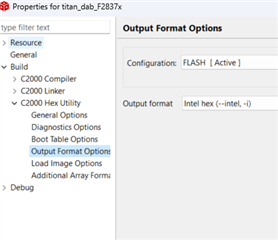

我使用十六进制实用程序让 CCS12自动生成十六进制输出、使用 Intel 格式

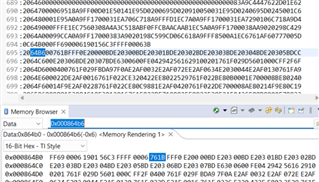

但是、当我查看生成的 Intel hex 文件时、例如我的 app.hex、它会显示如下所示:

:02000004 0008 F2 (第一行、起始地址的有效值为0x0008)

...

:20 64B6 0076FFE200E200E201E202E203E204E205E206E207E606FE2956290276025600FFE2

因此,根据英特尔格式定义,它表示从地址000864B6开始, 十六进制图像数据是76 ... 等等

地址000864B6位于闪存段 D 中。通常、该起始地址不与128位边界对齐。 但我要确保将 FLASHD 设置为在.cmd 文件中的所有位置对齐(8)。

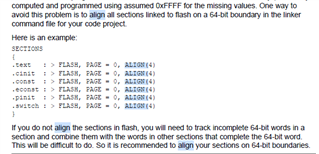

根据 spnu629a 文档、

我的理解是对于 align (4 )或(8)、闪存段中的内容应分别与64位或128位段对齐、即对于 align (8)、生成的映像十六进制的地址应始终从闪存中的 xxx8或 xxx0开始。 但基于这一点,我怀疑我的理解。

您能就我遗漏的内容提供一些建议吗? 或者、是否有办法强制生成的十六进制文件始终从 xxx8 / xxx0开始、即128位对齐、以简化闪存操作。

感谢您的帮助。

此致、

魏