您好!

我将 ADC 时钟预分频器配置为(输入时钟)/1.0 (意味着 ADCCLK = SYSCLK)我收到警告

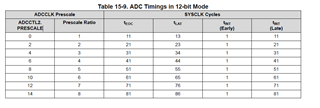

但它的工作,我通过获取时间戳来测量转换时间(CPUTimer )--> forceSOC --> while (ADC_isBusy(ADCA_BASE ))-->获取第二个 时间戳(CPUTimer ), 当 ADC 时钟预分频器更改为(输入时钟)/2.0时测量~23个时钟周期而不是~33个时钟周期 ;

如果 ADCCLK =(输入时钟)/2.0 (请参阅 ADC 指南中的向下示例)

此外、从 第1572页的 TMS320F28002x 实时微控制器(SPRUIN7C)数据表中、似乎可以选择 ADCCTL2.PRESCALE 0 (ADCCLK =SYSCLK ) 并将 tEOC 减少近一半:

我可以 使用我的设置吗? 如果不允许、那么为什么它只是警告而不是错误? 它是否会影响其他功能?

谢谢!

迈克尔