请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320F280039C-Q1 主题中讨论的其他器件:TIDM-02014

您好!

在由 TIDM-02014工程中的 syscfg 生成的 board.c 中、使用 epwm_setPhaseShift (resolver_exCITATION_PWM_BASE、2)将激励 PWM 的相移设置为"2"。

激励 PWM 配置为向上计数。

我做了几项修改、以便更好地将导致我的问题的担忧形象化。

- 我将 SYNC 输出脉冲配置为发送到 OUTPUTXBAR IO 以进行调试/监控。

- 我将 EPWM 配置为输出50%占空比波形、我可以在引脚上监测该波形。 我在 CNTR=ZERO 时使输出变为高电平、在 CNTR=CMPA 时使输出变为低电平(与其他示例中相同)。

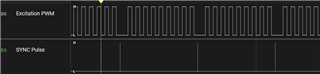

- 当我这么做时、我在激励 PMW 波形中看到缺少脉冲:

SYNC 会引起相负载并设置 CNTR=2、它没有这种 CNTR=ZERO 触发信号会使输出变为高电平。 我想这就是漏掉脉冲的原因。

在激励 PWM 的原始代码/设置中、中断触发也设置为 CNTR=ZERO board.c 中: EPWM_setADCTriggerSource (resolver_EXCITATION_PWM_BASE、EPWM_SOC_A、EPWM_SOC_TBCTR_ZERO);

此中断用于触发 DAC 的更新。 似乎在 SYNC 时也会错过 DAC 更新、因为当同步导致"2"加载到 CNTR 时会跳过 CNTR=ZERO。

这是正确的解释吗、即 DAC 更新丢失了?

如果愿意、遗漏 DAC 更新是否重要?

谢谢。