尊敬的 BU 专家:

我的客户正在使用 F28035进行变频和变占空比控制。 它们使用 HR 周期和占空比。

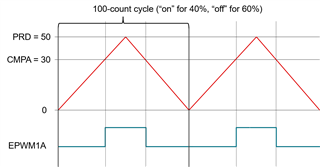

他们会发现、当 AQ 涉及 ZRO 或 PRD 时、输出会抖动。 当 AQ 仅涉及 CMP 时、没有抖动。 他们在 TRM 上找不到这方面的解释、您能帮忙解释一下吗?

同时、当在不改变占空比的情况下改变频率时、它们需要同时改变 PRD 和 CMP。 由于 F2803x 上没有全局加载但只有影子寄存器、因此如何保证 PRD 和 CMP 同时更新? 即使使用影子寄存器、当仅更新一个影子寄存器时、也可能发生从影子到活动状态的情况。

此致、

挂起。