Other Parts Discussed in Thread: TMS320F28075, TMS320F280037

主题中讨论的其他器件:TMS320F28075、

工具与软件:

数据表和 TRM 在很多地方都提到了"EPWMCLK"、我想知道它是什么。

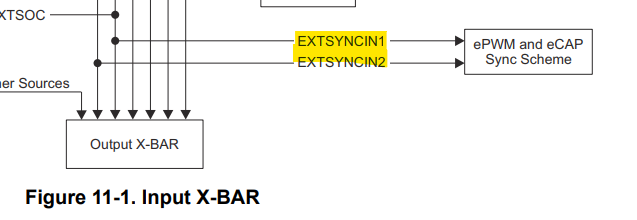

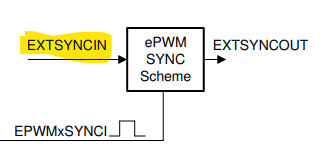

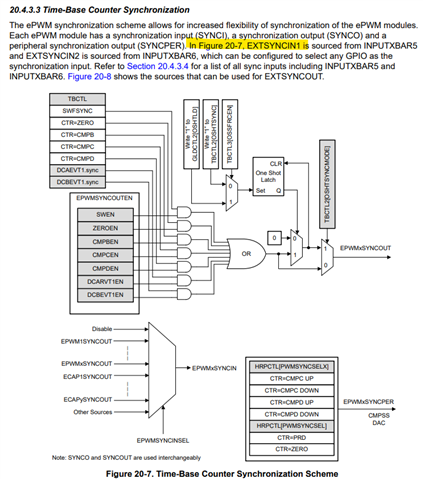

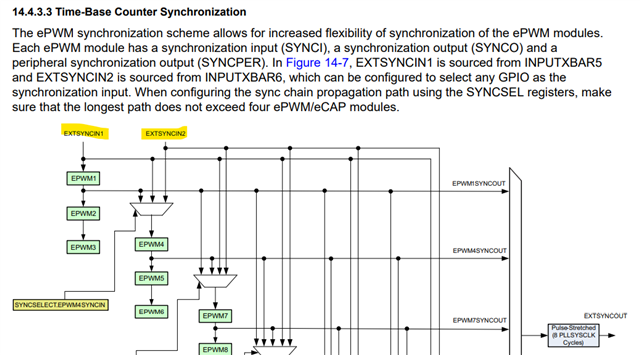

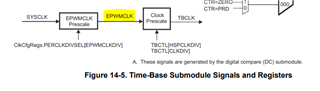

对于其它器件、例如 TMS320F28075、它非常明显、如下所示。

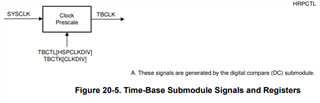

但是、TMS320F28003x TRM (spruiw9c.pdf)中的同一图未按如下方式显示。 (为 TBCT K [CLKDIV]拼写错误?)

上面显示的"时钟预分频"模块的控制位解释是:

>这些位选择时基时钟预分频值(TBCLK = EPWMCLK/(HSPCLKDIV * CLKDIV):

我可以将上面的"EPWMCLK"视为方框图中所示的 SYSCLK 吗?

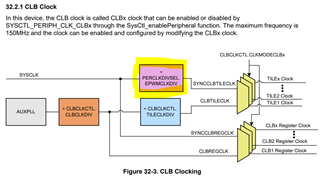

另外一个部件、我认为下图中的洋红色块可能需要移除?

此致、