工具与软件:

尊敬的 Champ:

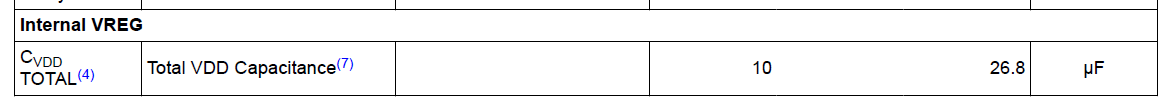

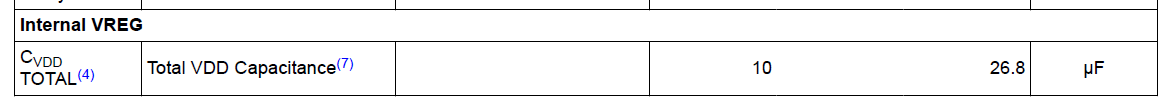

使用内部 VREG 时、CVDD 总电容应为10-26.8uF。

如何理解最大26.8uF 值的限制?

如果超过26.8uF、那么故障模式是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的 Champ:

使用内部 VREG 时、CVDD 总电容应为10-26.8uF。

如何理解最大26.8uF 值的限制?

如果超过26.8uF、那么故障模式是什么?

嗨、Huihuang

请参阅我们的硬件设计指南第3.4.1节" 去耦电容器背景的电源要求": https://www.ti.com/lit/an/spracz9a/spracz9a.pdf。

此致、

Allison

Huihuang

在我们增加 VDD 电源上的电容时、我们还将增加内部 LDO 在1.2V 电源开启时完全斜升所需的时间。 在得出 DS 中的值时、考虑到这一点以及内部 POR/BOR 何时基于 VDDIO 电源电平释放。 如果该值过大、则可能存在 XRSn 在1.2V 电压处于该电源轨的 DS 容差范围内之前被释放的风险。

如果客户已经在 VDD 网络上放置了更大的电容、他们可以在上电期间查看示波器上与 VDDIO/XRSn 上的电平、以查看上述情况是否存在任何风险。

此致!

Matthew