主题中讨论的其他器件:C2000WARE、 SysConfig

工具与软件:

您好!

我能够获得 biss 接口代码设置和 TI 的 CLA 启动代码、到目前为止一切都在工作。

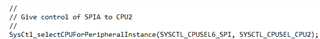

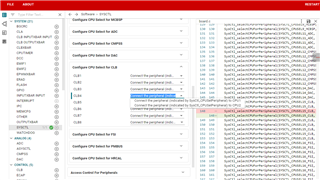

出于性能原因、我们希望在 CPU2上的 CLA 中运行 setup/start biss 接口、并触发 CPU1中的 SPI RX ISR。

我不建议重点关注 BiSS、实际上我们需要让 CPU2/CLA 启动 SPI 请求、并让 CPU1为 SPI RX ISR 提供服务。

我遇到的一个问题是、启动操作需要刷新 SPI 接口、CPU2需要拥有该接口? 其次、如果 CPU1需要处理 ISR 并使用 SPI、它如何将其取回。

这可能是关于如何使其发挥作用的任何建议都是很好的。

Dorion