工具与软件:

尊敬的团队:

我正在使用 TMS320F2812 DSP。 晶振30MHz、PLLCR=0x000A (即5倍)、时钟150MHz、和 XCLKOUT (引脚119)= 75MHz。

但有时在上电条件下、XCLKOUT 仅显示15MHZ。 即晶体值的一半。

在写入 PLLCR 寄存器后、我将提供所需的131072个周期延迟。

我一直在关注这个问题。 请解释在这个问题上 XPLLDIS、XRS、TRST 引脚的角色。

请帮助我解决此问题。

非常感谢

Praveen Vemula.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的团队:

我正在使用 TMS320F2812 DSP。 晶振30MHz、PLLCR=0x000A (即5倍)、时钟150MHz、和 XCLKOUT (引脚119)= 75MHz。

但有时在上电条件下、XCLKOUT 仅显示15MHZ。 即晶体值的一半。

在写入 PLLCR 寄存器后、我将提供所需的131072个周期延迟。

我一直在关注这个问题。 请解释在这个问题上 XPLLDIS、XRS、TRST 引脚的角色。

请帮助我解决此问题。

非常感谢

Praveen Vemula.

您好、普拉坦:

我想你完全错了。

您的声明 "如果 PLLCR 是0xA、这意味着 CLKIN 应该是 XTAL 频率。" 是错误的 .

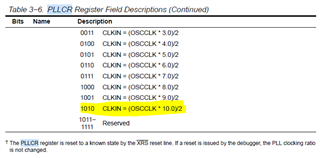

请参见突出显示的位说明1010=a,这意味着 OSCLK*10/2意味着时钟频率是晶体频率的5倍,按照我的第一个后 DTD。 29.8.4.200.

我的问题已在进行以下更改后得到解决:

1.上拉 XPPLDIS 引脚

2.下拉 TRST 引脚。

谢谢!

Praveen Vemula.