工具与软件:

尊敬的 Champ:

我要求为我的客户提供服务。

它们尝试使用比较器 和 EPWM DCAEVT1 / DCAEVT2、在一次性跳闸中触发 TZISR。

他们计划检查比较器输出状态并清除中的 TZ 一次性标志 另一个控制流 (不在 TZISR 中、即 在10kHz 定时器中断中 )、检查比较器输出是否为低电平、然后清除标志、然后在下一次触发 TZISR。

(1)。 在 上述情况下、 在 用户 确认比较器输出为低电平时、 比较器输出突然从低电平变为高电平、然后用户才能设置清除 TZ 标志的命令。 是否有机会这样做 导致在这种情况下未执行 TZISR? 是否需要考虑这里的时序?

(2)。 内部跳闸子模块机制如何检查一次性标志是否被清除? 检查每个 PWM 时钟周期(EPWMCLK)? 人们认为这将影响第一个问题的结果。

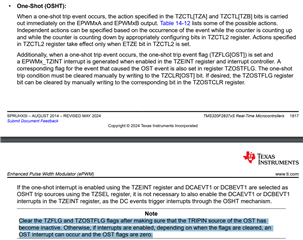

(3)。 在 TRM 中、它 ˟要锁存的条件、至少持续3 μ s TBCLK、如下所示。

(图1)

对于 TZx 输入低电平、DS 中针对脉冲持续时间指定的情况并不相同、对吧?

(图2)

˟不是如此、DS 中指定要锁存的最小3 μ s TBCLK 在哪里、或者只是 TRM 中的一条注意事项吗? 然后、 最小值在哪里 是否要考虑脉冲持续时间?

(4)。 对于通过 CMPSS 设置的 ePWM 一次性跳闸条件、确认估算的完成执行时间达到 TZISR 第一行、并考虑 ISR 或堆栈存储器上的中断延迟和等待状态、以获得额外的延迟。 专家是否会逐一明确列出? 从 CMPSS -> EPWM-Xbar -> EPWM 直流子模块-> TZISR (第一行代码)估算的执行时间。

谢谢。此致、

Johnny