主题中讨论的其他器件:SysConfig

工具与软件:

尊敬的 Champs:

我是为我们的客户提出这个问题。

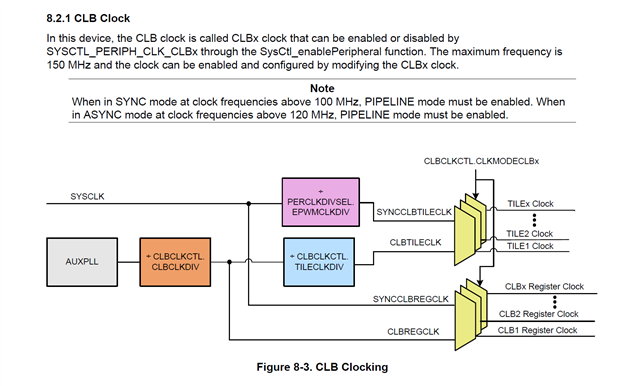

当用户使用 SYSCLK = EPWMCLK = 200 MHz 时、这是否意味着在 TRM 的8.2.1 CLB 时钟中 CLB 时钟不能超过150 MHz 时、CLB 时钟可以最大为100 MHz?

(请注意、SYSCLK = EPWMCLK = 200 MHz 是这里的硬性要求。)

问题1:

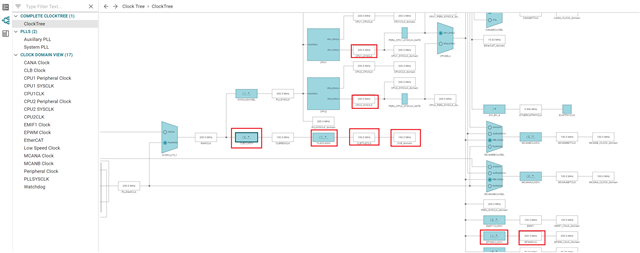

我们使用下面的 SysConfig Clocktree。

您是否请确认下面的配置正确?

问题2:

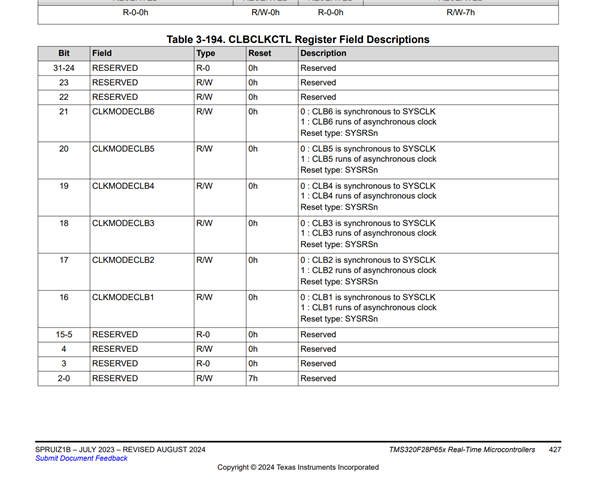

在下面的 TRM 表3-194中、对于 CLBCLKCTL、这些位被保留。 用户看不到 CLBCLKDIV、TILECLKDIV。

出什么问题了吗?

通过使用上面的 SysConfig 时钟树、可以正确设置 CLB 时钟吗?