工具与软件:

在双有源电桥控制应用中、当相移计数器值从超前突然变为滞后(从0.5-1变为0-0.5或相反)时、转换器对脉冲跳跃事件非常敏感。 我希望采用一种权变措施来 减轻这种影响。

当跟随者 PWM 通道上发生同步事件时、我想要:

检查相位值是否介于0和0.25*TBPRD -->设置 OUTA 并清除 OUTB

或者 检查相位值是否介于0.75*TBPRD 和1*TBPRD -->清除 OUTA 并设置 OUTB 之间

通过读取/写入寄存器是否实际上可以实现上述功能?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

在双有源电桥控制应用中、当相移计数器值从超前突然变为滞后(从0.5-1变为0-0.5或相反)时、转换器对脉冲跳跃事件非常敏感。 我希望采用一种权变措施来 减轻这种影响。

当跟随者 PWM 通道上发生同步事件时、我想要:

检查相位值是否介于0和0.25*TBPRD -->设置 OUTA 并清除 OUTB

或者 检查相位值是否介于0.75*TBPRD 和1*TBPRD -->清除 OUTA 并设置 OUTB 之间

通过读取/写入寄存器是否实际上可以实现上述功能?

Patrick、您好!

我怀疑这个问题与我在下面的主题中所描述的一样。 请参阅以下内容、如果他们 能够解决您的问题、请告诉我

此致、

Allison

您好!

我正在使用 Simulink 编码器、但我能够在主循环中插入一个 C 函数、以允许代码在每个周期执行。 GPIO 仅用于诊断。 我认为我没有正确设置 TZ 功能。

PWM5配置了相位控制与 PWM1、只有在将相位从前导(0到0.5*PRD)更改为滞后(0.5*PRD 到1*PRD)或其他方向(由于计数器值跳过 CMP 阈值)时、才会发生脉冲跳跃、如在您的示例中所示。

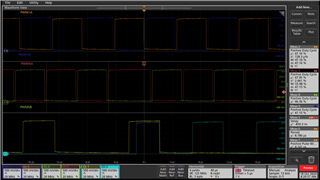

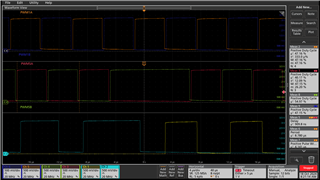

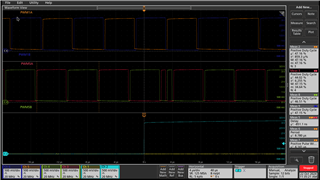

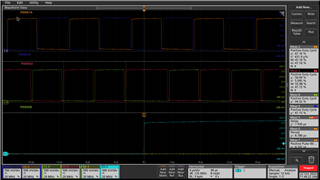

我包括一些屏幕截图的问题切换前置和滞后.

超前->滞后

滞后->超前

下面的脉冲跳跃检查功能

//

// Included Files

//

#include "pulseSkip.h"

#include "DAB_OpenLoop_f28379d_CAN.h"

#include "epwm.h"

#include "F2837xD_epwm.h"

#include "gpio.h"

#include "F2837xD_gpio.h"

extern volatile struct EPWM_REGS EPwm5Regs;

volatile struct EPWM_REGS * PWM5RegsPtr = &EPwm5Regs;

extern volatile struct GPIO_DATA_REGS GpioDataRegs;

volatile struct GPIO_DATA_REGS * GpioDataRegsPtr = &GpioDataRegs;

void pulseSkip(void)

{

// Read Registers

unsigned int Temp_CMPA = PWM5RegsPtr->CMPA.bit.CMPA;

unsigned int Temp_TBCTR = PWM5RegsPtr->TBCTR;

unsigned int Temp_TBPHS = PWM5RegsPtr->TBPHS.bit.TBPHS;

unsigned int Temp_TBPRD = PWM5RegsPtr->TBPRD;

bool tSYNCI = PWM5RegsPtr->TBSTS.bit.SYNCI;

if (tSYNCI == 1)

{

if (Temp_TBPHS > Temp_CMPA && Temp_TBCTR < Temp_CMPA)

{

EALLOW;

PWM5RegsPtr->TZSEL.bit.OSHT1 = 1;

PWM5RegsPtr->AQCTLA2.bit.T1U = 1;

PWM5RegsPtr->AQCTLB2.bit.T1U = 2;

GpioDataRegsPtr->GPFSET.bit.GPIO161 = 1;

EDIS;

}

else if (Temp_TBPHS < Temp_CMPA && Temp_TBCTR > Temp_CMPA)

{

EALLOW;

PWM5RegsPtr->TZSEL.bit.OSHT1 = 1;

PWM5RegsPtr->AQCTLA2.bit.T1U = 2;

PWM5RegsPtr->AQCTLB2.bit.T1U = 1;

GpioDataRegsPtr->GPFSET.bit.GPIO163 = 1;

EDIS;

}

else

{

EALLOW;

PWM5RegsPtr->TZSEL.bit.OSHT1 = 0;

PWM5RegsPtr->AQCTLA2.bit.T1U = 0;

PWM5RegsPtr->AQCTLB2.bit.T1U = 0;

PWM5RegsPtr->TZOSTCLR.bit.OST1 = 1;

PWM5RegsPtr->TZCLR.bit.OST = 1;

GpioDataRegsPtr->GPFCLEAR.bit.GPIO161 = 1;

GpioDataRegsPtr->GPFCLEAR.bit.GPIO163 = 1;

EDIS;

}

}

else if (Temp_TBCTR == 0 || Temp_TBCTR == Temp_CMPA || Temp_TBCTR == Temp_TBPRD)

{

EALLOW;

PWM5RegsPtr->TZSEL.bit.OSHT1 = 0;

PWM5RegsPtr->AQCTLA2.bit.T1U = 0;

PWM5RegsPtr->AQCTLB2.bit.T1U = 0;

PWM5RegsPtr->TZOSTCLR.bit.OST1 = 1;

PWM5RegsPtr->TZCLR.bit.OST = 1;

GpioDataRegsPtr->GPFCLEAR.bit.GPIO161 = 1;

GpioDataRegsPtr->GPFCLEAR.bit.GPIO163 = 1;

EDIS;

}

}

Patrick、您好!

我仍然不清楚您尝试使用单稳态跳闸的目的-您是否介意在此处详细说明所需的信号输出和单稳态跳闸的目的? 如果您有时间、或许快速绘制草图或图表会有所帮助。

另请注意、我所做的示例与是否发生同步无关、而是在 PWM 参数(CTR 与 CMP、vs PHS 等)适应同步脉冲会导致错过操作限定符的情况时立即主动更新动作限定符(尤其是 T1事件)。 不确定这是否会在时间上产生巨大影响、但您能尝试改用这种方式来实现吗?

除了 OST 设置之外,关于缺少 AQ 的解决方法的逻辑对我来说很好。 此外、如果我在那里漏掉了一些内容、您是否介意共享您的 PWM 初始化配置(计数模式、AQS 等)?

此致、

Allison

我尝试使用 OST 根据从超前到滞后或反向发生变化来强制设置或清除 PWM 输出。 我认为这是不可执行的,因为它似乎没有及时执行。 我再看一下您的示例代码、我以前不清楚。

更新了代码以供参考。 这种方法可行、但执行速度可能太慢、无法解决每个脉冲跳跃条件。

//

// Included Files

//

#include "pulseSkip.h"

#include "DAB_OpenLoop_f28379d_CAN.h"

#include "epwm.h"

#include "F2837xD_epwm.h"

#include "gpio.h"

#include "F2837xD_gpio.h"

extern volatile struct EPWM_REGS EPwm5Regs;

volatile struct EPWM_REGS * PWM5RegsPtr = &EPwm5Regs;

extern volatile struct GPIO_DATA_REGS GpioDataRegs;

volatile struct GPIO_DATA_REGS * GpioDataRegsPtr = &GpioDataRegs;

unsigned int Prev_TBPHS, Prev_TBCTR;

bool up_flag, down_flag;

void pulseSkip(void)

{

// Read Registers

unsigned int Temp_CMPA = PWM5RegsPtr->CMPA.bit.CMPA;

unsigned int Temp_TBCTR = PWM5RegsPtr->TBCTR;

unsigned int Temp_TBPHS = PWM5RegsPtr->TBPHS.bit.TBPHS;

unsigned int Temp_TBPRD = PWM5RegsPtr->TBPRD;

bool tSYNCI = PWM5RegsPtr->TBSTS.bit.SYNCI;

bool Temp_TZFLG = PWM5RegsPtr->TZFLG.bit.OST;

if (up_flag == 0 && down_flag == 0)

{

if (Prev_TBPHS < Temp_CMPA && Temp_TBPHS > Temp_CMPA)

{

PWM5RegsPtr->AQTSRCSEL.bit.T1SEL = 0b0111;

EALLOW;

PWM5RegsPtr->TZSEL.bit.OSHT1 = 1;

PWM5RegsPtr->TZCTL.bit.TZA = 0b10;

PWM5RegsPtr->TZCTL.bit.TZB = 0b01;

GpioDataRegsPtr->GPFSET.bit.GPIO161 = 1;

EDIS;

up_flag = 1;

}

else if (Prev_TBPHS > Temp_CMPA && Temp_TBPHS < Temp_CMPA)

{

PWM5RegsPtr->AQTSRCSEL.bit.T1SEL = 0b0111;

EALLOW;

PWM5RegsPtr->TZSEL.bit.OSHT1 = 1;

PWM5RegsPtr->TZCTL.bit.TZA = 0b01;

PWM5RegsPtr->TZCTL.bit.TZB = 0b10;

GpioDataRegsPtr->GPFSET.bit.GPIO163 = 1;

EDIS;

down_flag = 1;

}

}

if (Temp_TZFLG == 1 && up_flag == 1)

{

if (Prev_TBCTR <= Temp_TBPRD && Temp_TBCTR > 0x0000)

{

EALLOW;

PWM5RegsPtr->TZSEL.bit.OSHT1 = 0;

PWM5RegsPtr->TZCTL.bit.TZA = 0b11;

PWM5RegsPtr->TZCTL.bit.TZB = 0b11;

PWM5RegsPtr->TZOSTCLR.bit.OST1 = 1;

PWM5RegsPtr->TZCLR.bit.OST = 1;

GpioDataRegsPtr->GPFCLEAR.bit.GPIO161 = 1;

EDIS;

up_flag = 0;

}

}

if (Temp_TZFLG == 1 && down_flag == 1)

{

if (Prev_TBCTR <= Temp_CMPA && Temp_TBCTR > Temp_CMPA)

{

EALLOW;

PWM5RegsPtr->TZSEL.bit.OSHT1 = 0;

PWM5RegsPtr->TZCTL.bit.TZA = 0b11;

PWM5RegsPtr->TZCTL.bit.TZB = 0b11;

PWM5RegsPtr->TZOSTCLR.bit.OST1 = 1;

PWM5RegsPtr->TZCLR.bit.OST = 1;

GpioDataRegsPtr->GPFCLEAR.bit.GPIO163 = 1;

EDIS;

down_flag = 0;

}

}

Prev_TBPHS = Temp_TBPHS;

Prev_TBCTR = Temp_TBCTR;

}

我还尝试在此处编译 PWM 配置。 这是一个基本递增计数器、ePWM1作为载波、ePWM5作为具有可变相移值 TBPHS (初始为零)的跟随器。

// ePWM1

EPwm1Regs.TBCTL.all = (EPwm1Regs.TBCTL.all & ~0x3FFFU) | 0x10U;

EPwm1Regs.TBCTL2.all = (EPwm1Regs.TBCTL2.all & ~0xC000U) | 0x0U;

EPwm1Regs.TBPRD = 877U; // Time Base Period Register

EPwm1Regs.TBPHS.all = (EPwm1Regs.TBPHS.all & ~0xFFFF0000U) | 0x0U;

EPwm1Regs.CMPCTL.all = (EPwm1Regs.CMPCTL.all & ~0x3C5FU) | 0x0U;

EPwm1Regs.CMPCTL2.all = (EPwm1Regs.CMPCTL2.all & ~0x3C5FU) | 0x0U;

EPwm1Regs.CMPA.bit.CMPA = 438U; // Counter Compare A Register

EPwm1Regs.AQCTLA.all = 154U;

EPwm1Regs.AQCTLB.all = 101U;

EPwm1Regs.AQSFRC.all = (EPwm1Regs.AQSFRC.all & ~0xC0U) | 0xC0U;

EPwm1Regs.AQCSFRC.all = (EPwm1Regs.AQCSFRC.all & ~0xFU) | 0x5U;

EPwm1Regs.DBCTL.all = (EPwm1Regs.DBCTL.all & ~0x8FFFU) | 0x8C0BU;

EPwm1Regs.DBRED.bit.DBRED = (uint16_T)(50.0);

EPwm1Regs.DBFED.bit.DBFED = (uint16_T)(50.0);

EPwm1Regs.ETSEL.all = (EPwm1Regs.ETSEL.all & ~0xFF7FU) | 0x1909U;

EPwm1Regs.ETPS.all = (EPwm1Regs.ETPS.all & ~0x30U) | 0x30U;

EPwm1Regs.ETSOCPS.all = (EPwm1Regs.ETSOCPS.all & ~0xF0FU) | 0x102U;

EPwm1Regs.ETINTPS.all = (EPwm1Regs.ETINTPS.all & ~0xFU) | 0x1U;

EPwm1Regs.PCCTL.all = (EPwm1Regs.PCCTL.all & ~0x7FFU) | 0x0U;

EALLOW;

EPwm1Regs.TZSEL.all = 0U; // Trip Zone Select Register

EPwm1Regs.TZCTL.all = (EPwm1Regs.TZCTL.all & ~0xFFFU) | 0xFFFU;

EPwm1Regs.TZEINT.all = (EPwm1Regs.TZEINT.all & ~0x7EU) | 0x0U;

EPwm1Regs.DCACTL.all = (EPwm1Regs.DCACTL.all & ~0x30FU) | 0x4U;

EPwm1Regs.DCBCTL.all = (EPwm1Regs.DCBCTL.all & ~0x30FU) | 0x0U;

EPwm1Regs.DCTRIPSEL.all = (EPwm1Regs.DCTRIPSEL.all & ~ 0xFFFFU) | 0x0U;

EPwm1Regs.TZDCSEL.all = (EPwm1Regs.TZDCSEL.all & ~0xFFFU) | 0x0U;

EPwm1Regs.DCFCTL.all = (EPwm1Regs.DCFCTL.all & ~0x3FU) | 0x10U;

EPwm1Regs.DCFOFFSET = 0U; // Digital Compare Filter Offset Register

EPwm1Regs.DCFWINDOW = 0U; // Digital Compare Filter Window Register

EPwm1Regs.DCCAPCTL.all = (EPwm1Regs.DCCAPCTL.all & ~0x1U) | 0x0U;

EPwm1Regs.HRCNFG.all = (EPwm1Regs.HRCNFG.all & ~0xA0U) | 0x0U;

EPwm1Regs.EPWMXLINK.bit.TBPRDLINK = 0U;

EPwm1Regs.EPWMXLINK.bit.CMPALINK = 0U;

EPwm1Regs.EPWMXLINK.bit.CMPBLINK = 0U;

EPwm1Regs.EPWMXLINK.bit.CMPCLINK = 0U;

EPwm1Regs.EPWMXLINK.bit.CMPDLINK = 0U;

EPwm1Regs.HRPCTL.all = (EPwm1Regs.HRPCTL.all & ~0x72U) | 0x0U;

EDIS;

// ePWM5

EPwm5Regs.TBCTL.all = (EPwm5Regs.TBCTL.all & ~0x3FFFU) | 0x4U;

EPwm5Regs.TBCTL2.all = (EPwm5Regs.TBCTL2.all & ~0xC000U) | 0x0U;

EPwm5Regs.TBPRD = 877U; // Time Base Period Register

EPwm5Regs.TBPHS.all = (EPwm5Regs.TBPHS.all & ~0xFFFF0000U) | 0x0U;

EPwm5Regs.CMPCTL.all = (EPwm5Regs.CMPCTL.all & ~0x3C5FU) | 0x0U;

EPwm5Regs.CMPCTL2.all = (EPwm5Regs.CMPCTL2.all & ~0x3C5FU) | 0x0U;

EPwm5Regs.CMPA.bit.CMPA = 438U; // Counter Compare A Register

EPwm5Regs.CMPB.bit.CMPB = 32000U; // Counter Compare B Register

EPwm5Regs.CMPC = 32000U; // Counter Compare C Register

EPwm5Regs.CMPD = 32000U; // Counter Compare D Register

EPwm5Regs.AQCTLA.all = 154U;

EPwm5Regs.AQCTLB.all = 101U;

EPwm5Regs.AQSFRC.all = (EPwm5Regs.AQSFRC.all & ~0xC0U) | 0xC0U;

EPwm5Regs.AQCSFRC.all = (EPwm5Regs.AQCSFRC.all & ~0xFU) | 0x5U;

EPwm5Regs.DBCTL.all = (EPwm5Regs.DBCTL.all & ~0x8FFFU) | 0x8C0BU;

EPwm5Regs.DBRED.bit.DBRED = (uint16_T)(50.0);

EPwm5Regs.DBFED.bit.DBFED = (uint16_T)(50.0);

EPwm5Regs.ETSEL.all = (EPwm5Regs.ETSEL.all & ~0xFF7FU) | 0x1101U;

EPwm5Regs.ETPS.all = (EPwm5Regs.ETPS.all & ~0x30U) | 0x30U;

EPwm5Regs.ETSOCPS.all = (EPwm5Regs.ETSOCPS.all & ~0xF0FU) | 0x101U;

EPwm5Regs.ETINTPS.all = (EPwm5Regs.ETINTPS.all & ~0xFU) | 0x1U;

EPwm5Regs.PCCTL.all = (EPwm5Regs.PCCTL.all & ~0x7FFU) | 0x0U;

EALLOW;

EPwm5Regs.TZSEL.all = 0U; // Trip Zone Select Register

EPwm5Regs.TZCTL.all = (EPwm5Regs.TZCTL.all & ~0xFFFU) | 0xFFFU;

EPwm5Regs.TZEINT.all = (EPwm5Regs.TZEINT.all & ~0x7EU) | 0x0U;

EPwm5Regs.DCACTL.all = (EPwm5Regs.DCACTL.all & ~0x30FU) | 0x4U;

EPwm5Regs.DCBCTL.all = (EPwm5Regs.DCBCTL.all & ~0x30FU) | 0x0U;

EPwm5Regs.DCTRIPSEL.all = (EPwm5Regs.DCTRIPSEL.all & ~ 0xFFFFU) | 0x0U;

EPwm5Regs.TZDCSEL.all = (EPwm5Regs.TZDCSEL.all & ~0xFFFU) | 0x0U;

EPwm5Regs.DCFCTL.all = (EPwm5Regs.DCFCTL.all & ~0x3FU) | 0x10U;

EPwm5Regs.DCFOFFSET = 0U; // Digital Compare Filter Offset Register

EPwm5Regs.DCFWINDOW = 0U; // Digital Compare Filter Window Register

EPwm5Regs.DCCAPCTL.all = (EPwm5Regs.DCCAPCTL.all & ~0x1U) | 0x0U;

EPwm5Regs.HRCNFG.all = (EPwm5Regs.HRCNFG.all & ~0xA0U) | 0x0U;

EPwm5Regs.EPWMXLINK.bit.TBPRDLINK = 4U;

EPwm5Regs.EPWMXLINK.bit.CMPALINK = 4U;

EPwm5Regs.EPWMXLINK.bit.CMPBLINK = 4U;

EPwm5Regs.EPWMXLINK.bit.CMPCLINK = 4U;

EPwm5Regs.EPWMXLINK.bit.CMPDLINK = 4U;

EPwm5Regs.HRPCTL.all = (EPwm5Regs.HRPCTL.all & ~0x72U) | 0x0U;

EDIS;您好、Allison、

我在另一线程中实现了您的解决方案、但使用直接寄存器写入。 我想它已经部分解决了这个问题。 我不清楚 T1 AQ 的动作是如何工作的、因为对于 AQCTLx2寄存器和行为没有很多示例或文档。 也许您可以给我指一个信息来源、以便我能够更好地理解。 然而、当 TBPHS 状态更改(低于或高于 CMPA)发生在 SYNCI 脉冲之后或之前超过半个周期之后、仍然存在问题、这意味着 PWM1和 PWM5在一个周期内存在很大的不平衡。 这将导致糟糕的转换器行为。 请告诉我您的想法。

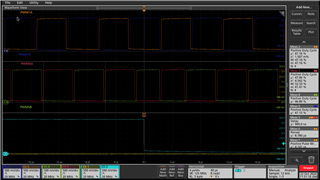

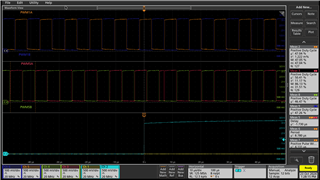

我在此附上了主循环中 pulseSkip 函数的屏幕截图和代码。

//

// Included Files

//

#include "pulseSkip.h"

#include "DAB_OpenLoop_f28379d_CAN.h"

#include "epwm.h"

#include "F2837xD_epwm.h"

#include "gpio.h"

#include "F2837xD_gpio.h"

extern volatile struct EPWM_REGS EPwm5Regs;

volatile struct EPWM_REGS * PWM5RegsPtr = &EPwm5Regs;

extern volatile struct GPIO_DATA_REGS GpioDataRegs;

volatile struct GPIO_DATA_REGS * GpioDataRegsPtr = &GpioDataRegs;

void pulseSkip(void)

{

// Read Registers

unsigned int Temp_CMPA = PWM5RegsPtr->CMPA.bit.CMPA;

unsigned int Temp_TBPHS = PWM5RegsPtr->TBPHS.bit.TBPHS;

if (Temp_TBPHS > Temp_CMPA)

{

PWM5RegsPtr->AQTSRCSEL.bit.T1SEL = 7;

PWM5RegsPtr->AQCTLA2.bit.T1U = 1;

PWM5RegsPtr->AQCTLB2.bit.T1U = 2;

GpioDataRegsPtr->GPFSET.bit.GPIO161 = 1;

}

else

{

PWM5RegsPtr->AQTSRCSEL.bit.T1SEL = 7;

PWM5RegsPtr->AQCTLA2.bit.T1U = 2;

PWM5RegsPtr->AQCTLB2.bit.T1U = 1;

GpioDataRegsPtr->GPFCLEAR.bit.GPIO161 = 1;

}

}

良好的行为、PHS 开关(高->低)就在 SYNCI -达到粗略对称性之前

不良行为、 PHS 开关(高电平->低电平)在 SYNCI 之前超过半个周期

良好的行为、PHS 开关(低->高)就在 SYNCI -达到粗略对称性之前

不良行为、PHS 开关(低电平->高电平)在 SYNCI 之前超过半个周期

Patrick、您好!

很抱歉耽误你的时间。 遗憾的是、我还没有为这个分配太多时间、但在我看来、 权变措施案例需要添加到这些时间/针对这些时间进行调整。 关于 T1/T2、它们的作用类似于任何其他动作限定符(例如、CMPA 上为高电平、CMPA 上为低电平。但可配置为其他 PWM 事件、除了 CTR 匹配某个值外、也与 CMP 计数器比较值相同)。 例如、TRM 提到您可以具有基于 比较器事件、跳闸或同步输入事件的 PWM 操作限定符(您应该在此处使用其中的后者作为权变措施)。

我会在一周结束前仔细检查并提供量身定制的回复、但我要做的是看看 TBPHS、CTR、 和 CMP 值、并查看权变措施中是否存在差距、应使用 T1/T2覆盖跳过的操作(顺便说一下、如果尚未这样做、您可以使用输出 XBAR 示波器探测到引脚的同步输出信号、这有助于提高可见性)。 如果您能在此期间进行评估、请告诉我。 欣赏灵活性!

此致、

Allison

感谢您到目前为止的帮助。

我相信我通过以下代码解决了该问题。 基本上、我通过 更改 T1寄存器将 TBPHS 的设置尽可能接近同步。 该函数将命令的 PHS 值作为输入、CMPA/PER 是固定的。 模块以1ms 的速率运行。

//

// Included Files

//

#include "updatePWM.h"

extern volatile struct EPWM_REGS EPwm1Regs;

volatile struct EPWM_REGS * PWM1RegsPtr = &EPwm1Regs;

extern volatile struct EPWM_REGS EPwm5Regs;

volatile struct EPWM_REGS * PWM5RegsPtr = &EPwm5Regs;

extern volatile struct GPIO_DATA_REGS GpioDataRegs;

volatile struct GPIO_DATA_REGS * GpioDataRegsPtr = &GpioDataRegs;

unsigned int Prev_PWM5_PHS = 0;

unsigned int PWM1_PER = 877;

unsigned int PWM5_PER = 877;

unsigned int PWM1_CMPA = 438;

unsigned int PWM5_CMPA = 438;

unsigned int PWM5_PHS = 0;

bool Enable = 0;

//bool up_flag, down_flag;

void updatePWM(unsigned int PHS, bool EN)

{

// Read Registers

PWM1_PER = 877;

PWM5_PER = 877;

PWM1_CMPA = 439;

PWM5_CMPA = 439;

PWM5_PHS = PHS;

Enable = EN;

/*

Propagate PHS changes to the appropriate registers and also set up

T1 to correct for pulse skipping instances.

Set diagnostic output bit to show when the PHS value changes.

*/

if (PWM5_PHS != Prev_PWM5_PHS)

{

GpioDataRegsPtr->GPBSET.bit.GPIO32 = 1;

if (PWM5_PHS > PWM5_CMPA)

{

PWM5RegsPtr->AQCTLA2.bit.T1U = 0b0001;

PWM5RegsPtr->AQCTLB2.bit.T1U = 0b0010;

}

else if (PWM5_PHS < PWM5_CMPA)

{

PWM5RegsPtr->AQCTLA2.bit.T1U = 0b0010;

PWM5RegsPtr->AQCTLB2.bit.T1U = 0b0001;

}

PWM5RegsPtr->TBPHS.bit.TBPHS = PWM5_PHS;

}

else

{

GpioDataRegsPtr->GPBCLEAR.bit.GPIO32 = 1;

PWM5RegsPtr->AQCTLA2.bit.T1U = 0b0000;

PWM5RegsPtr->AQCTLB2.bit.T1U = 0b0000;

}

// Store the previous value of PHS to check for changes.

Prev_PWM5_PHS = PWM5_PHS;

}

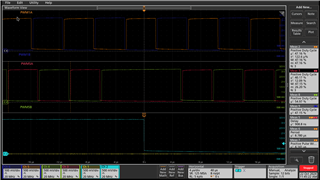

我还有一个仍在尝试解决的边缘情况。 我显示了下面的屏幕截图。 如果将 PHS 从前置值(0.2*TBPRD)设置为 TBPRD 值本身(几乎没有相移)、我会在 PWMA 中得到干扰。 这仅在将 TBPHS 设置为 TBPRD 时发生、没有其他情况。

对于 OUT A、我的 AQ 设置在 PRD 上、在 CMP 上清零、对于 OUT B、反之亦然。死区设置为50个周期。 也许您有一些想法?

Patrick、您好!

很高兴听到进度! 明天我回到办公室时、我们再看一遍。不过、这听起来可能是另一个具有 PWM 参数的临界情况、你是否已经在实施 TBPHS = TBPRD 的权变措施案例? 通常、设置 TBPHS = TBPRD 不应导致错过的动作限定符。 在这种情况下、似乎您已将 T1配置为在 TBPHS = TBPRD 的同时、在 SYNC 上将 EPWM5A 驱动为低电平。 我认为 、这会导致在计数器加载 TBPHS (=TBPRD) 以再次将信号设置为高电平之前、对于一个小脉冲、已经很高的 EPWM5A 会清零。 请告诉我您是否能够修改代码以适应这种情况。

为了澄清、在这些示波器截图中、蓝色信号指示 TBPHS 值更新? 您是否也在查看与同步脉冲相关的这些信号?

此致、

Allison

蓝色信号是 GPIO32、当 TBPHS 发生变化时、我会设置该值以触发示波器。

同步发生在 CTR = ZRO 时。 我确实尝试了针对 TBPHS=TBPRD 实施权变措施、但它导致了其他问题。 请告诉我,如果你有任何建议如何处理这一问题,我将尝试解决。

我将按如下方式初始化 AQ。 其他情况下无操作。 也许我应该重新配置以在 ZRO 采取行动? 还是将 SYNCO 调整为 PRD?

AQCTLA。 PRD = 2.

AQCTLA。 CAU = 1

AQCTLB。 PRD = 1

AQCTLB。 CAU = 2.