工具与软件:

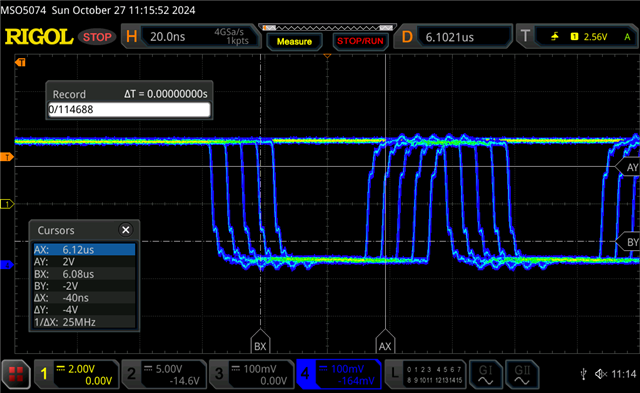

您好-我有一个应用、其中使用接收到的 FSI 帧来触发 FSI 帧传输。 FSI RX 标签匹配信号通过无逻辑的 CLB 直接路由、然后通过 CLB 输出交叉开关连接到引脚、再返回到输入 XBAR、再连接到 FSI TX 外部触发器。 通过这种配置、我可以观察 GPIO 引脚上的触发信号与开始数据传输之间的非确定性时序。 下面的捕获是在 GPIO FSI 触发信号中触发的、显示了 FSI TX 数据线且存在一定程度的持久性。 有5个间隔为5ns 的区域边沿、这似乎表明发送器将外部触发信号同步到 PLLRAWCLK (200MHz)、然后会有一些延迟直到下一个 TXCLK (20MHz)边沿。 鉴于 分布式同步是 FSI 接口的明显用例之一、这种非确定性行为似乎非常不可取。 在此用例中、是否有 FSI 配置可实现确定性延迟?

谢谢!

标记