Thread 中讨论的其他器件:C2000WARE

工具与软件:

文件路径:C:\ti\c2000\C2000Ware_5_01_00_00\libraries\boot_rom\f28003x\rev0\rom_sources\F28003x_rom\bootrom\include\cpu1brom_pbist。 h

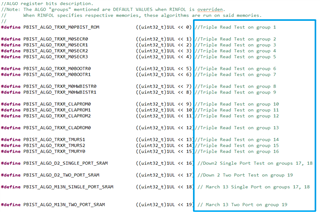

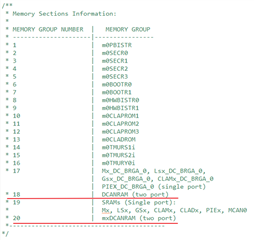

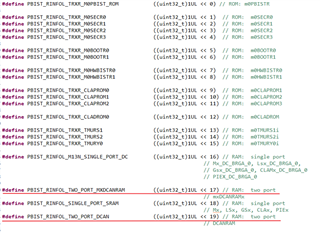

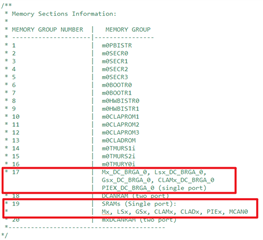

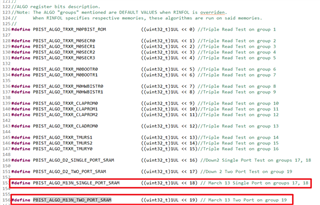

问题1:存储器组的描述与 define 不一致。 存储器组18是 DCANRAM (两端口)、存储器组20是 mxDCANRAM (两端口)、但是定义中的18是 mxDCANRAMx、而20是 DCANRAM。 你可以看看图片。

问题2:存储器组17和存储器组19之间的关系是什么

问题3:描述 define PBIST_ALGO_M13N_SINGLE_PORT_SRAM 中的组17、18上的3月13日单端口。 单端口算法可用于测试双端口存储器、因此该测试应该没有问题。 define PBIST_ALGO_M13N_TWO_PORT_SRAM 中介绍了3月13日组19上的两个端口、但组19是单端口 SRAM。 这里似乎有一个问题。

问题4:为什么 PBIST 没有测试所有 RAM?