工具与软件:

在上面的票据中、"16的 RAMPDECVAL 将导致每1个 SYSCLK 发生1LSB 的比较值变化"、但是我在数据表中发现 DAC 的稳定时间为1us、我的问题是 DAC 是否可以接受如此频繁的 RAMPDECVAL 更新?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

在上面的票据中、"16的 RAMPDECVAL 将导致每1个 SYSCLK 发生1LSB 的比较值变化"、但是我在数据表中发现 DAC 的稳定时间为1us、我的问题是 DAC 是否可以接受如此频繁的 RAMPDECVAL 更新?

嗨、Echo

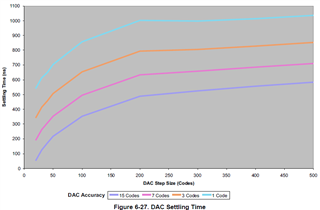

[报价 userid="592186" url="~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1440246/tms320f280049c-rampdecval-of-16-will-lead-to-a-1lsb-change-in-compdac-value-every-1-sysclk-conflicts-with-dac-settle-time/5527204 #5527204"]"16的 RAMPDECVAL 将导致每1个 SYSCLK Compdac 值发生1LSB 变化。" 在本文中、 RAMPDECVAL 的1LSB 变化值为16*1 SYSCLK、即80ns 或160ns、因此 DAC 的稳定时间1LSB 变化应小于此时间、对吗?每1个 SYSCLK 1LSB 是简单的配置值、但 DAC 稳定时间应该低于这些值、您可以在下图中看到作为我们之前的一个器件的参考、但我们尚未更新12位 DAC 的图

另一个问题是 DAC 的采样率是多少? 换句话说、DAC 在不丢失数据的情况下可以接受的 DACVALS 的最大变化率是多少?

您系统中所需的最高控制环路频率是多少? DAC 应足以满足大多数所需的环路频率

此致、

Peter