工具与软件:

您好!

我正在使用来自 CLB 生成的时钟的 SPI 时钟(SPI-CLK)设置 SPI 外设。

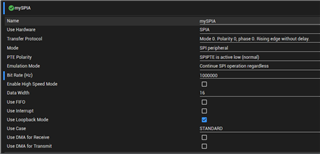

为了测试此配置、我尝试使用 SPI 环回模式。 SPI 设置显示在附加的配置映像中。

以下是我的设置的详细信息:

- 我已经通过 CLB 生成时钟(1MHz)、并通过 GPIO 将该信号连接到 SPI CLK 引脚。

- SPI PTE 引脚也通过 GPIO 接地。

- 我使用示波器监控所有这些信号。

当 SPI 处于控制器/主模式时、在 CLB 时钟与 SPI CLK 引脚断开连接的情况下、环回正常工作。

但是、当我将 SPI 切换到外设模式并将 CLB 时钟连接到 SPI CLK 引脚时、SPI POCI 引脚(MISO)保持高电平。 我已经验证了 SPI TXBUF 和 SPIDAT 寄存器的内容。 而 SPI TXBUF 显示预期值时、SPIDAT 的读数始终为0xFFFF。

非常感谢您对可能导致此问题的原因有任何见解。

是否可以在外设模式下使用环回模式和 SPI?

谢谢!

此致、

Wilko.