Other Parts Discussed in Thread: C2000WARE

Thread 中讨论的其他器件:C2000WARE

工具与软件:

我正在为 F28388S 设计引导加载程序。

我想通过 SCI 等下载使用 Teraterm 等的程序(无需更改引导模式)。

我希望在使用仿真器下载内部闪存时、通过分离内部闪存的扇区来开发引导加载程序。

我认为这种方法可行吗??

是否有任何值得参考的示例或文档????

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: C2000WARE

工具与软件:

我正在为 F28388S 设计引导加载程序。

我想通过 SCI 等下载使用 Teraterm 等的程序(无需更改引导模式)。

我希望在使用仿真器下载内部闪存时、通过分离内部闪存的扇区来开发引导加载程序。

我认为这种方法可行吗??

是否有任何值得参考的示例或文档????

谢谢你。

您好!

您所描述的方法是可行的。

我们有一份 串行闪存编程应用手册 可供您参考、C2000ware SDK 中还有示例代码。 有关串行闪存内核示例、请参阅 \driverlib\f2838x\examples\c28x_dual\flash_kernel

关于定制引导加载程序的一般信息、 C2000ware 中提供了引导 ROM 源代码(器件引导加载程序)、网址为 \libraries\boot_rom\f2838x\revA\rom_sources\CPU1\f2838x_rom\bootrom\source。 在开发自定义引导加载程序时、可以参考这些内容。

此致、

Matt

您好!

是的、一个到应用程序存储器地址的长分支(LB)汇编调用应该合适(假定您希望在一个 CPU 上运行并且从一个基于 RAM 的引导加载程序跳转到闪存)。 C28x CPU 和指令集的第217页 提供了有关 LB 的更多详细信息以供参考。

此致!

Matt

感谢您的回答。

我会检查您提供的信息。

目前、我已经确认可以使用我使用仿真器设计的引导加载程序来擦除和写入应用程序。 (通过调试模式下的存储器浏览器)但是、当下载闪存引导模式下的应用程序时、此程序不会写入内部闪存。 问题可能是什么???

此外、我应该如何设置要下载的应用文件? 我是否需要在 CCS 工程-> Properties -> C2000 Hex Utility 中设置任何内容? 目前、输出格式设置为 Intel hex。

您好!

您是否正在尝试使用引导 ROM 中的 SCI 引导加载程序、或者将自定义引导加载程序加载到闪存中、然后引导至闪存?

此外、如何设置要下载的应用程序文件

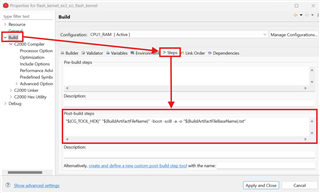

对于 SCI 引导、您需要添加以下编译后处理步骤(在 CCS project -> Properties -> Build -> Steps 下)。 应用文件 需要在引导模式下格式化、表源为 SCI-A 端口、8位模式和 ASCII 十六进制输出。

"${CG_TOOL_HEX}" "${BuildArtifactFileName}" -boot -sci8 -a -o "${BuildArtifactFileBaseName}.txt"

此致!

Matt

1.删除内部闪存地址0x88000之后区域的函数、地址0x88000之后下载应用程序的函数、跳转到下载的程序的函数。 从 CCS 下载 CCS 工程(自定义引导加载程序)-通过 SCI 通信连接到 Teraterm、并输入密钥执行该功能。

2.自定义引导加载程序现在通过电源复位引导至闪存引导模式。

3.在加载的自定义引导加载程序中删除地址0x88000之后的数据并下载应用程序。

4.下载完成后,跳转至程序执行应用程序。

以上是我所想到的场景。

1、本文第一个问题是我认为的情形是否可能,

2.我询问在创建应用程序时是否需要设置任何设置,例如使用 T.I.3提供的串行闪存编程器时。 此外、当我运行使用 CCS 中的仿真器设计的文件时、我确认闪存存储器被删除并且程序被下载。 但是、当在闪存引导模式下引导并运行自定义引导加载程序时、闪存存储器似乎被删除、但不会进行下载。 有什么问题吗???

很抱歉我缺少信息、但感谢您继续回答。

__attribute__((ramfunc))

void eraseSector (uint32_t 扇区)、

__attribute__((ramfunc))

void downloadApplication()

我可以只在我想像上面一样在 RAM 中运行的函数前面添加__attribute__((ramfunc))吗???

我在使用 API 的函数前面添加了__attribute__((ramfunc))。

您好!

除了链接器 cmd 文件外、以下是其他一些需要检查的事项:

此致!

Matt

按照您的建议、文件在闪存模式下无法工作的现象消失了。

当使用仿真器运行应用程序并将存储在 Memory Browser 中的值和输出格式设置为 Array (--array)时、它似乎与应用程序的 Memory Browser 相同。 如果您选择不同的选项、即使您解释数据帧、它似乎也不同。 创建输出文件时、我是否需要额外设置任何内容??? 我想就此部分提供建议。

谢谢你。

您好!

您使用数组输出格式的具体原因是什么?

对于 SCI 引导、您需要添加以下编译后处理步骤(在 CCS project -> Properties -> Build -> Steps 下)。 应用文件 需要在引导模式下格式化、表源为 SCI-A 端口、8位模式和 ASCII 十六进制输出。 [报价]您尝试对 SCI 引导的方式是否正确? 您应该使用上述的应用格式(这是 TI SCI 闪存编程器的格式)。

此致!

Matt

您好!

根据我的理解、您有一个自定义 SCI 引导加载程序、可以使用 Tera Term 下载和运行应用程序。 您的 Tera Term 配置设置是什么?

如果您选择了不同的选项、即使您解释数据帧、也会有不同之处。

您要选择哪些不同的选项? Memory Browser 中似乎有何不同?

《汇编语言工具用户指南》 提供了有关十六进制实用程序输出选项的更多详细信息 、您也可以参考这些选项。

此致!

Matt

你好

首先、我将应用程序的输出格式设置为 Array、并通过自定义引导加载程序完成下载。

我尝试了 asm (" LB 0x088000");此命令跳转到应用程序、但出现了 ESTOP0。

C:/Users\~~\f2838x_CPU1_bootloader_20241128.out:{3}0x3fe96f{4}"中的"_system_post_cinit ()"没有可用的源代码

ESTOP0与上面的标识一起出现。 如何解决此问题?

我还附加了应用 CMD 文件。

CLA_SCRATCHPAD_SIZE = 0x100;

--undef_sym=__cla_scratchpad_end

--undef_sym=__cla_scratchpad_start

MEMORY

{

/* BEGIN is used for the "boot to Flash" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000002

BOOT_RSVD : origin = 0x000002, length = 0x0001AF /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x0001B1, length = 0x00024F

RAMM1 : origin = 0x000400, length = 0x0003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x0007F8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMD0 : origin = 0x00C000, length = 0x000800

RAMD1 : origin = 0x00C800, length = 0x000800

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS14 : origin = 0x008800, length = 0x002000

// RAMLS1 : origin = 0x008800, length = 0x000800

// RAMLS2 : origin = 0x009000, length = 0x000800

// RAMLS3 : origin = 0x009800, length = 0x000800

// RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS57 : origin = 0x00A800, length = 0x001800

// RAMLS6 : origin = 0x00B000, length = 0x000800

// RAMLS7 : origin = 0x00B800, length = 0x000800

RAMGS0 : origin = 0x00D000, length = 0x001000

RAMGS1 : origin = 0x00E000, length = 0x001000

RAMGS2 : origin = 0x00F000, length = 0x001000

RAMGS3 : origin = 0x010000, length = 0x001000

RAMGS4 : origin = 0x011000, length = 0x001000

RAMGS5 : origin = 0x012000, length = 0x001000

RAMGS610 : origin = 0x013000, length = 0x005000

// RAMGS7 : origin = 0x014000, length = 0x001000

// RAMGS8 : origin = 0x015000, length = 0x001000

// RAMGS9 : origin = 0x016000, length = 0x001000

// RAMGS10 : origin = 0x017000, length = 0x001000

RAMGS11 : origin = 0x018000, length = 0x001000

RAMGS125 : origin = 0x019000, length = 0x003FF8

// RAMGS13 : origin = 0x01A000, length = 0x001000

// RAMGS14 : origin = 0x01B000, length = 0x001000

// RAMGS15 : origin = 0x01C000, length = 0x000FF8

// RAMGS15_RSVD : origin = 0x01CFF8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* Flash sectors */

FLASH0 : origin = 0x080002, length = 0x001FFE /* on-chip Flash */

FLASH1 : origin = 0x082000, length = 0x002000 /* on-chip Flash */

FLASH2 : origin = 0x084000, length = 0x002000 /* on-chip Flash */

FLASH3 : origin = 0x086000, length = 0x002000 /* on-chip Flash */

FLASH4_start : origin = 0x088000, length = 0x000002 /* on-chip Flash */

FLASH4 : origin = 0x088002, length = 0x007FFD /* on-chip Flash */

FLASH5 : origin = 0x090000, length = 0x008000 /* on-chip Flash */

FLASH6 : origin = 0x098000, length = 0x008000 /* on-chip Flash */

FLASH7 : origin = 0x0A0000, length = 0x008000 /* on-chip Flash */

FLASH8 : origin = 0x0A8000, length = 0x008000 /* on-chip Flash */

FLASH9 : origin = 0x0B0000, length = 0x008000 /* on-chip Flash */

FLASH10 : origin = 0x0B8000, length = 0x002000 /* on-chip Flash */

FLASH11 : origin = 0x0BA000, length = 0x002000 /* on-chip Flash */

FLASH12 : origin = 0x0BC000, length = 0x002000 /* on-chip Flash */

FLASH13 : origin = 0x0BE000, length = 0x001FF0 /* on-chip Flash */

// FLASH13_RSVD : origin = 0x0BFFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

CPU1TOCPU2RAM : origin = 0x03A000, length = 0x000800

CPU2TOCPU1RAM : origin = 0x03B000, length = 0x000800

CPUTOCMRAM : origin = 0x039000, length = 0x000200

CMTOCPURAM : origin = 0x038000, length = 0x000200

CPUTOCMRAM_ECAT : origin = 0x039200, length = 0x000200

CMTOCPURAM_ECAT : origin = 0x038200, length = 0x000200

CANA_MSG_RAM : origin = 0x049000, length = 0x000800

CANB_MSG_RAM : origin = 0x04B000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

CLA1_DMA_MSGRAM : origin = 0x001680, length = 0x000080

DMA_CLA1_MSGRAM : origin = 0x001700, length = 0x000080

}

SECTIONS

{

codestart : > FLASH4_start, ALIGN(8)

.text : >> FLASH4, ALIGN(8)

.cinit : > FLASH4, ALIGN(8)

.switch : > FLASH4, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMLS57

#if defined(__TI_EABI__)

.init_array : > FLASH4, ALIGN(8)

.bss : > RAMGS125

.bss:output : > RAMLS57

.data : > RAMLS57

.sysmem : > RAMLS57

/* Initalized sections go in Flash */

.const : > FLASH4, ALIGN(8)

#else

.pinit : > FLASH4, ALIGN(8)

.ebss : > RAMLS57

.esysmem : > RAMLS57

/* Initalized sections go in Flash */

.econst : >> FLASH5, ALIGN(8)

#endif

MSGRAM_CPU1_TO_CPU2 : > CPU1TOCPU2RAM, type=NOINIT

MSGRAM_CPU2_TO_CPU1 : > CPU2TOCPU1RAM, type=NOINIT

MSGRAM_CPU_TO_CM : > CPUTOCMRAM, type=NOINIT

MSGRAM_CM_TO_CPU : > CMTOCPURAM, type=NOINIT

MSGRAM_CPU_TO_CM_ECAT > CPUTOCMRAM_ECAT, type=NOINIT

MSGRAM_CM_TO_CPU_ECAT > CMTOCPURAM_ECAT, type=NOINIT

dclfuncs : > FLASH6, ALIGN(8)

/* CLA specific sections */

#if defined(__TI_EABI__)

Cla1Prog : LOAD = FLASH4,

RUN = RAMLS57,

LOAD_START(Cla1funcsLoadStart),

LOAD_END(Cla1funcsLoadEnd),

RUN_START(Cla1funcsRunStart),

LOAD_SIZE(Cla1funcsLoadSize),

ALIGN(8)

#else

Cla1Prog : LOAD = FLASH4,

RUN = RAMLS57,

LOAD_START(_Cla1funcsLoadStart),

LOAD_END(_Cla1funcsLoadEnd),

RUN_START(_Cla1funcsRunStart),

LOAD_SIZE(_Cla1funcsLoadSize),

ALIGN(8)

#endif

CLADataLS0 : > RAMLS57

CLADataLS1 : > RAMLS57

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW, type=NOINIT

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH, type=NOINIT

Cla1ToDmaMsgRAM : > CLA1_DMA_MSGRAM, type=NOINIT

DmaToCla1MsgRAM : > DMA_CLA1_MSGRAM, type=NOINIT

Cla1DataRam : >> RAMLS57

/* CLA C compiler sections */

//

// Must be allocated to memory the CLA has write access to

//

CLAscratch :

{ *.obj(CLAscratch)

. += CLA_SCRATCHPAD_SIZE;

*.obj(CLAscratch_end) } > RAMLS57

.scratchpad : > RAMLS57

.bss_cla : > RAMLS57

cla_shared : > RAMLS57

#if defined(__TI_EABI__)

.const_cla : LOAD = FLASH4,

RUN = RAMLS57,

RUN_START(Cla1ConstRunStart),

LOAD_START(Cla1ConstLoadStart),

LOAD_SIZE(Cla1ConstLoadSize)

#else

.const_cla : LOAD = FLASH4,

RUN = RAMLS57,

RUN_START(_Cla1ConstRunStart),

LOAD_START(_Cla1ConstLoadStart),

LOAD_SIZE(_Cla1ConstLoadSize)

#endif

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASH4,

RUN = RAMGS610,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASH4,

RUN = RAMGS610,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

您好!

看起来你 在.out 文件中有一个定制的_system_post_cinit 函数。 编译器中提供的标准_system_post_cinit 函数是空函数。 请检查您的函数实现、并检查导致 ESTOP0的条件。

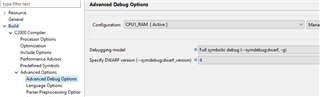

您的.out 是使用-g 选项构建的吗? 否则、CCS 在调试时无法链接 C 源文件、并可能导致出现"No source available for...(无可用源)"问题。 建议使用-g 选项构建工程、以查看和调试 C 文件。 如果不是、您可以反汇编调试。

可以在项目属性中设置-g 选项:

此致、

Veena.

您好!

应用程序不能简单地通过分支执行???

是的、通过分支到应用的代码开始来执行应用。

您能 分享一下吗 .map 项目构建的输出、以便我们可以检查0x82487和0x8A487位置处的内容?

此外、您的引导加载程序是否有自己的链接器 CMD 文件?

此致!

Matt

您好!

您是否能够通过 CCS 正常加载应用? 您是否还可以共享存储器浏览器在地址0x80000和0x88000处的屏幕截图以及如何从引导加载程序分支?

在自定义引导加载程序映射文件中、0x82487 位于 MSGRAM (MSGRAM_CPU2_TO_CPU1)中。 如果能够跳转到应用程序入口点、但之后有一个指向 MSGRAM 的 LB、因此应用链接器肯定出现了问题。

此致!

Matt