请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320F280038C-Q1 工具与软件:

大家好、TI 团队。

我有一些问题 ERRORSTS 引脚 TMS320F280038C-Q1的优势。

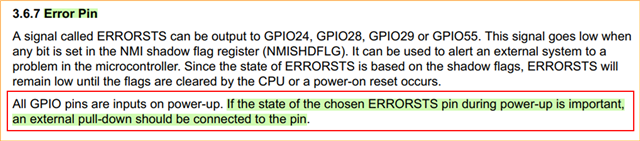

从" TMS320F28003x 实时微控制器 技术参考手册"中、错误引脚的说明为 '如果上电期间所选 ERRORSTS 引脚的状态很重要、则应将外部下拉电阻连接到该引脚。' 如下所示。

我对上面的句子有一些疑问。

1. 为什么即使该引脚作为低电平有效运行、ERRORSTS 引脚也应该是外部下拉?

2. 我们考虑 MCU 引脚映射处的 ERRORSTS 引脚。

如果我们尝试 将 ERRORSTS 引脚实现为低电平有效、是否可以将此引脚连接到外部上拉电阻器?

我需要 澄清电路的设计原理图。

如果你们给我一些答案、我将不胜感激。

提前感谢您。

此致、

李承根