主题中讨论的其他器件: PMP23216、 TMS320F280039C

工具与软件:

您好!

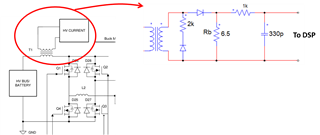

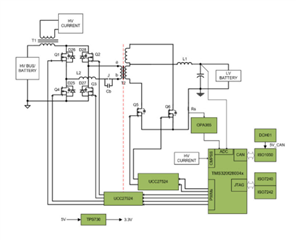

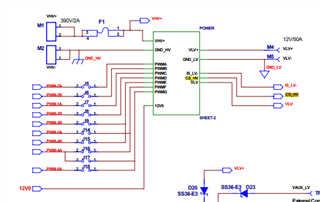

我们正在设计一个 3kW 直流/直流电源转换器 基于 TIDM-02000参考设计 、并且在期间我们遇到了问题 老化实验 . 转换器在运行大约一段时间后出现短路 30分钟 操作条件下的 RMS 电流。

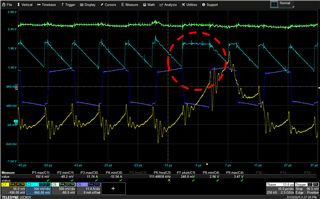

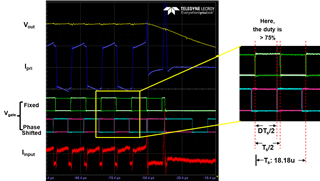

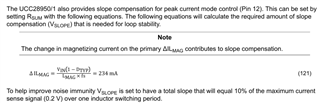

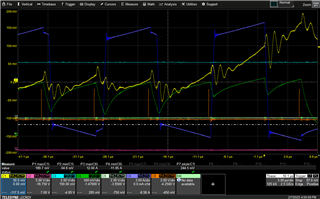

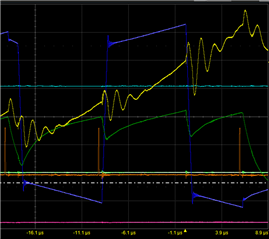

下面是在发生短路之前捕获的波形:

蓝色波形 :变压器初级电流(Ipri)。

红色波形 :输入电流(I_Ininput )

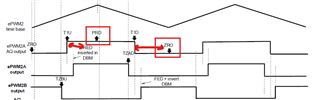

的符号 图 1. 就在短路之前、我们观察到 粉色门控信号 无法早于关闭 浅绿色门控信号 、正如预期的那样。

我们怀疑短路是由引起的 斜坡补偿不足 . 目前、斜率值已设置为 13. . 我们将斜率补偿值增加到 23. 、这延长了运行时间。 但是、转换器在持续时间较长(短路)后仍会跳闸。 因此、我们的结论是、 斜坡补偿可能仍然不足、但其他问题是不能排除的。

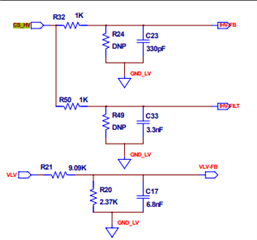

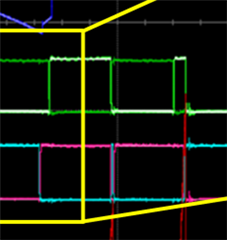

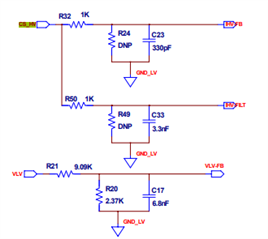

从中删除 TI 参考设计手册(PMP23216、第11页) 提供了以下有关斜率补偿的信息

![]()

在另一个参考设计中(slua560d)(UCC28950 600W 相移全桥设计评审/应用报告(修订版 D))

斜率值根据磁化电流的变化来确定。

我的具体问题是:

1. 短路现象是否是斜坡补偿不足造成的?

上述公式是否适用于计算基于 TIDM-02000的 拓扑的斜率补偿斜坡(请注意、 Ipri 用作控制变量而不是电感器电流)?

µs 以安培/μ s 为单位计算斜率后、如何缩放该值并将其应用以在 DAC 中生成斜坡(8位 DAC 的范围为0–255)?

4. 是否有更准确或更理论的方法来确定所需的 PSFB 斜率补偿值?

感谢您提供有关计算和应用正确斜率补偿值的指导、以及有关短路的其他潜在原因的任何见解。

提前感谢您的支持。

此致

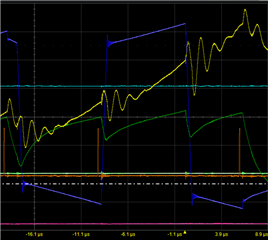

<Blue:itr (pri)、 Orange:

<Blue:itr (pri)、 Orange: