工具与软件:

尊敬的 Champ:

我要求为我的客户提供服务。

他们正在 使用 F28P659DK8PTPQ1 (176引脚)器件进行硬件设计。

(1)。 我是否可以再次确认、此封装上的引脚92,146,148均可配置为 ERRORSTS 引脚、正确?

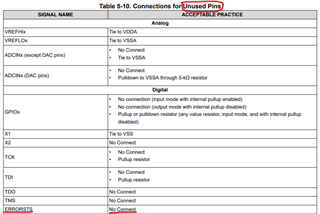

(2)。 如果 引脚 92,146,148不希望用作 ERRORSTS 引脚、即用作通用输入/输出。 从硬件设计来看、 并不需要外部下拉电阻、对吧?

(3)。 默认情况下、引脚92,146,148应全部设置为 GPIO (GPIO 多路复用引脚、复位= 0)。 在 TRM 中、是 IT 器件 提到过

ERRORSTS 引脚处于 tri 状态(高阻抗)、直到芯片电源轨上升到较低的工作限值。

问题是, 在用户手动配置 main ()中的引脚之前,并不是每一个 GPIO 在器件上电时都保持高阻抗,为什么我们特别强调这一说法? ERRORSTS 引脚(引脚 92,146,148)与普通 GPIO 引脚是否有任何差异?

谢谢。此致、

Johnny