Other Parts Discussed in Thread: CDCM6208

工具/软件:

TI 团队大家好、

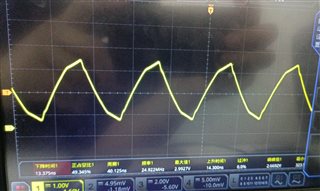

我在时钟分配设计中使用 CDCM6208、我观察到一种奇怪的行为:PLL 间歇性锁定、然后在操作过程中反复解锁。 该PLL_UNLOCK引脚会随着时间的推移在高电平和低电平之间切换、表示 PLL 正在环路中进入和退出锁定状态。

以下是我的配置的详细信息:

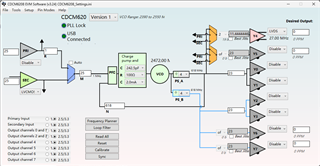

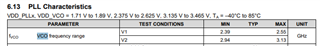

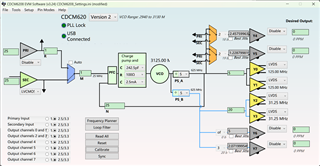

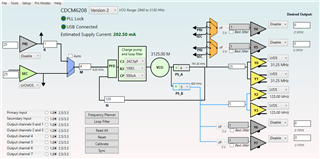

Register 0: 01B7 Register 1: 0060 Register 2: 02CD Register 3: 00F0 Register 4: 30AB Register 5: 0001 Register 6: 0016 Register 7: 0001 Register 8: 0016 Register 9: 0203 Register 10: 00A7 Register 11: 1C72 Register 12: 0001 Register 13: 0160 Register 14: 0000 Register 15: 0051 Register 16: 0160 Register 17: 0000 Register 18: 0051 Register 19: 0160 Register 20: 0000 Register 21: 0000 Register 40: 0000 Inputs: Primary Input Frequency: 25 Secondary Input Frequency: 25 Version 1 C1: 100p R2: 500 C2: 22n R3: 100 C3: 242.5p Charge Pump: 2m

STATUS0: