主题中讨论的其他器件:LMK05318BEVM

工具/软件:

大家好!

我正在使用 LMK05318BEVM 进行一个定制电路板原型测试。 我们使用此 DPLL 以不同的频率运行所有必需部分(如以太网 PHY、ADC 和 DAC)。

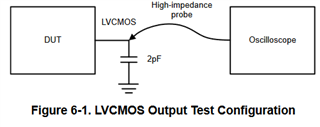

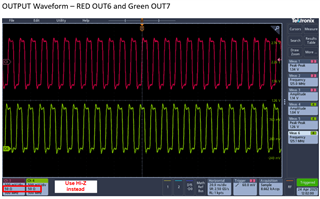

因此、要在 LMK05318BEVM 上测试 LVCMOS 输出、我们使用 TICSPRO 工具来配置所需的通道、如6和7。 我们观察到电压电平高达1.1V。但根据数据表、电压电平应为1.8V。 您能帮助解决这个问题吗?

作为 LVCMOS 输出之一、我们将其用作一个 GPIO 上的触发器。该 GPIO 需要最低1.2V VIH 电平来对 DAC/ADC 过程进行采样、但由于输出电压电平较低、我们无法在该 GPIO 上生成触发器。