主题中讨论的其他器件: OPA211

工具/软件:

尊敬的 TI 团队:

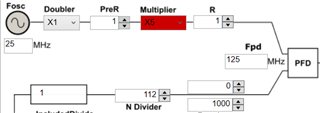

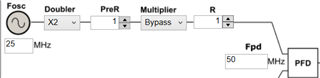

我目前正在使用 LMX2594设计和评估电路。 在我的配置中、

VCO1在8GHz 下振荡、并分频至输出2GHz。

我有以下问题:

1.根据 VCO1的振荡范围(7.5G-8.6GHz)和91.6MHz (Kvco /V)、

我计算出、Vtune 端子电压应为大约5.46V 以实现8GHz 振荡。

但是、在测量实际器件时、该电压仅在1.3V 左右。

器件的这种正常运行吗?

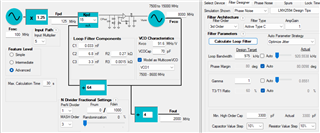

2.我使用 PLLatinum Sim 设计了环路滤波器、选择了三阶有源 Type C、目标环路带宽为975kHz。

我使用计算得出的元件值和 OPA211运算放大器来实现电路。

遗憾的是、OPA211输出表现出振荡。

虽然我已经通过调整 C3和 R3来抑制这种振荡、

我想知道哪款运算放大器更适合与 PLLatinum Sim 计算出的原始元件值配合使用。

我随附了 PLLatinum Sim 设计文件、供您参考有关元件值。

注意:我已将文件扩展名从.sim 更改为.txt、因为系统不允许上传扩展名为.sim 的文件。

e2e.ti.com/.../lmx2594_5F00_design.txt

此致、

松本市