工具/软件:

我希望使用主 LMK04828生成7.8125M 时钟、并将其输入到两个 LMK04828芯片的 in0端口、以实现多板同步。

我测试的两个从机器的时钟基本是同步的、但频率似乎不稳定、抖动很大

主/从 LMK 电路原理图、从 LMK 仅使用板上的100M 晶体振荡器和主 LMK 的 IN0-7.8125M 输出

主机 LMK 的7.8125M 输出与有源 LMK 的输出同步、无抖动、并通过等长同轴电缆连接到从 LMK 的 in0端口

从器件 LMK 的输出500m 被偏置并产生抖动

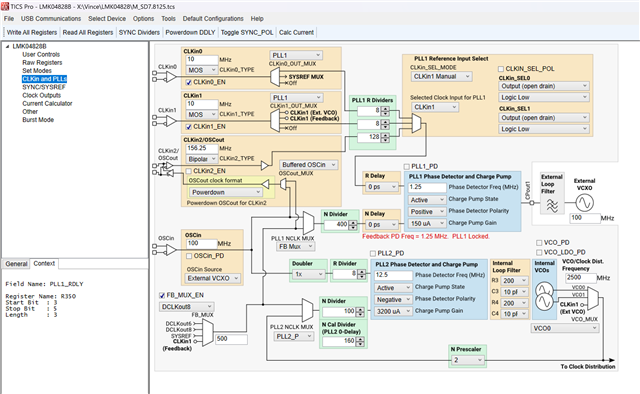

e2e.ti.com/.../in0_5F00_SD7.8125.tcs

从机器的配置文件

我不太清楚多板时钟同步的配置。 我希望你可以指导和帮助我!