Other Parts Discussed in Thread: LMK04208, LMX2594

主题( LMX2594)中讨论的其他器件

工具/软件:

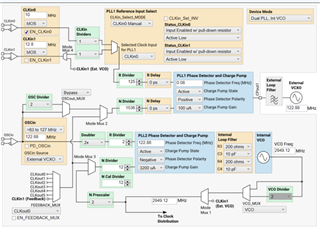

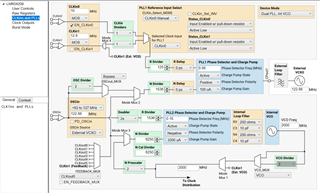

大家好、我们正在研究一种利用 LMK04208来创建100MHz 信号的设计。 122.88MHz 处有一个10MHz 输入和一个 VCXO。

使用 TICS Pro 通过此配置对 LMK 进行编程的 Im:

该配置的寄存器如下:

R0 (INIT) 0x00160040

R0 0x00140280

R1 0x00143201

R2 0x00143202

R3 0x00140323

R4 0x00143204

R5 0x00143205

R6 0x01100006

R7 0x01600007

R8 0x01010008

R9 0x5555549

R10 0x9102410A

R11 0x0401900B

R12 0x1BCC006C

R13 0x1B02802D

R14 0x0230000E

R15 0x8000800F

R16 0xC1550410

R24 0x00000018

R25 0x02C0FA19

0xAR26 FA8001A

R27 0x10001F5B

R28 0x6001801C

R29 0x01830D5D

R30 0x02030D5E

R31 0x000C001F

我们正在与一个可以在其他频率下工作的制造商主板合作、但我似乎无法锁定该频率。

电路板附带演示设置、可获取12.8MHz 并输出122.88MHz。 我不知道它在我的设计中是存在相位问题、甚至可能在这些频率下工作。 有什么想法发生了什么?