工具/软件:

您好、

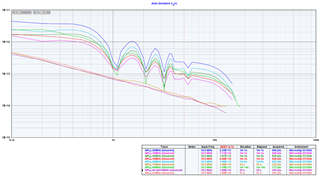

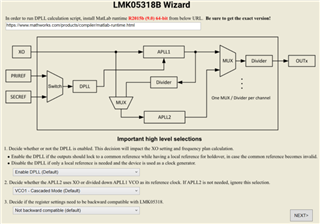

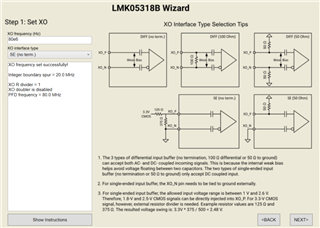

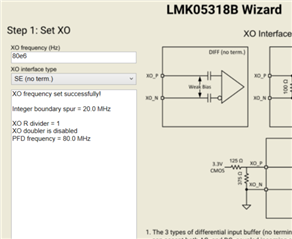

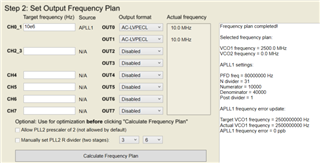

我正在测试 LMK05318BEVM 以生成时钟。 芯片在 APLL 模式下运行、输入由信号发生器 SDG6022X 生成(我将 J9更改为短接引脚2-3、以使用外部 XO 基准、其他插孔保持在默认位置)。 我尝试生成高质量、高精度且稳定的10MHz 输出。 不过、我发现当输入信号恰好位于40MHz、60MHz、80MHz 时、输出频率稳定性会显著下降。 您可以在下面看到 Allan 偏差图、在80MHz 输入端、有很多粗糙的频率噪声、而在80.2846MHz 输入端(只是任意值)具有平滑且稳定的频率。

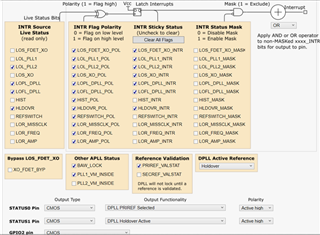

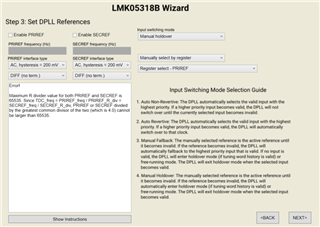

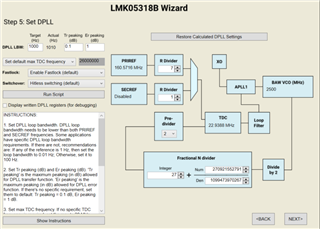

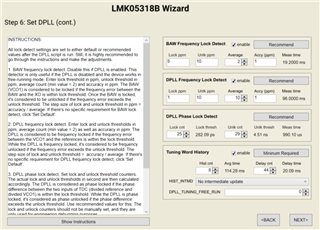

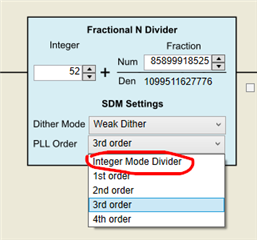

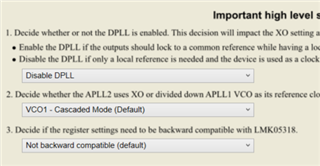

此处显示了 TICS 软件设置、默认设置其他高级 APLL 参数。

您知道为什么会出现此问题吗?

谢谢您、

Noah