부품 번호:LMX2594

도구 μ 소프트웨어 μ s:

尊敬的 TI:

我想我之前已经询问过这一点。

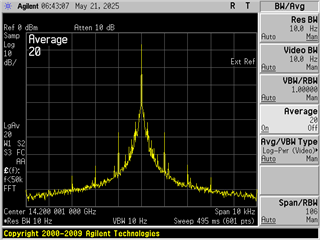

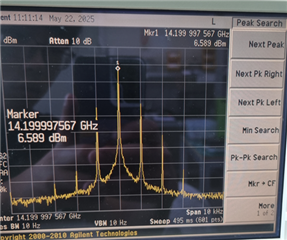

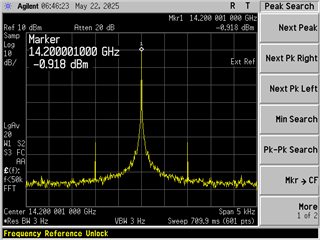

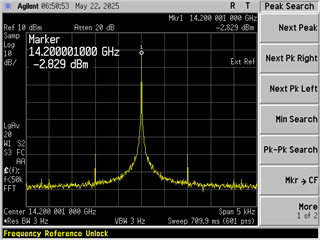

目前、当我将频率设置为14200.001 MHz 时、可以观察到随附图中显示的小数杂散。

配置如下。

由于无法修改环路滤波器、因此必须通过软件来解决问题。

我已经尝试更改了 MOD 值、MASH 顺序和 MASH SEED、但这些调整没有影响。

(环路滤波器与 EVB 板上的滤波器相同。)

有没有办法改进这一点?

如果当前值为:

-

Fpfd :100 MHz

-

FRAC : 1 / 修改 :100000

然后将其更改为:

-

FRAC :20,480 / 修改 :2,048,000,001.

在这种情况下、图中所示杂散是否不再出现?

BR、

Ko