主题:LMX2820中讨论的其他器件

工具/软件:

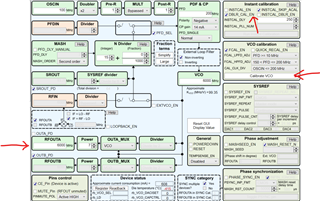

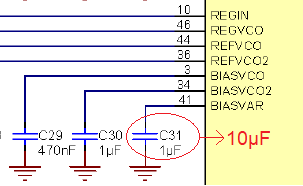

我刚开始 PLL 设计。 话虽如此、我使用 FSWP 相位噪声分析仪、使用 LMK61PDOA2评估板生成的100MHz 基准振荡器测试一组10GHz 至20GHz 范围内的5个频率、以驱动 LMX2820 EVM。 我使用单端配置、除了具有50欧姆端接的 RF_OUTN 外、还从参考中分流 OUTP、端接为50欧姆。 我将电源设置为3.3V、并运行 TICS PLL 寄存器写入控制器以设置所需的输出频率。 我在频谱分析仪上观察到信号以验证输出。

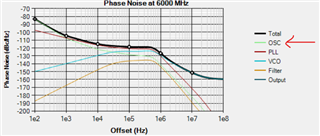

然后、我使用.5% RBW 和10kHz 至100MHz 偏移频率运行相位噪声分析仪。 与数据表相比、这会产生绝对垃圾。

这就是我期望通过即插即用方式获得数据表中定义的相位噪声的评估板。 我的一些想法是改用差分系统、从而改进 CMRR、因此如果接地平面上存在一些热电压、那么它将消除这种情况。 然后在 Platinum 中整理以找到最佳配置。 但是、默认设置是否应该已经是最佳设置? Im 在较高频率下还观察到大量杂散。

如果我可以提供任何其他信息来帮助解决此问题、请告诉我。 谢谢!!