Other Parts Discussed in Thread: LMK6H

工具/软件:

尊敬的团队:

对于 LMK6H、HCSL (100MHz) 型 LKM6H 器件的数据表中列出了大量抖动测量结果。

我只是想知道不同的封装 (DLE ANN DLF) 和不同的 VDD(与不同的 VOH 相关)是否 会使抖动结果不同? 您是否有要分享的详细测试条件?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Tim:

封装尺寸对 LMK6H 抖动性能没有重大影响。 对于数据表规格、典型条件通常在 VDD = 3.3V 和 25C 时确定、但最大规格考虑了 PVT 范围内的最坏情况变化。

特别是对于 PCIe 抖动规格、最小值和最大值还包括 接收器处模拟 PLL 环路滤波器设置扫描结果的变化。 如需了解更多详细信息、请参阅我们的 LMK6H PCIe 合规性报告: https://www.ti.com/lit/an/snla445/snla445.pdf

此致、

Connor

尊敬的 Connor:

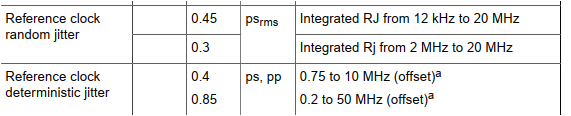

我也在寻找

(1) 随机抖动(从 12 kHz 到 20MHz 的集成 RJ)

(2) 随机抖动(从 2MHz 到<xmt-block1> 20MHz</xmt-block> 的集成 RJ)</s> 20MHz

(3) 确定性抖动((0.75 至 10MHz(偏移) )

(4) 确定性抖动((0.2 到 50MHz(偏移))

您是否知道如何在数据表中找到它们?